云实验平台使用指南

第七章 云实验平台使用指南

这一章是云实验平台的使用指南。如果不做大组的扩展实验(即实验6)的话,基于云的实验平台已经足够同学们使用了。

总体介绍

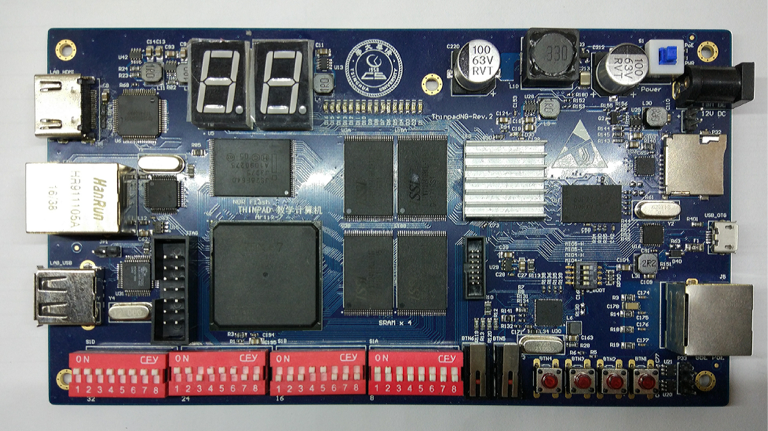

THINPAD-Cloud教学计算机实验平台是清华大学计算机科学与技术系为计算机系统类课程教学实验专门设计的。实验平台的设计目标充分考虑了完整计算机系统设计和实现的需要,以现场可编程逻辑电路(FPGA)为核心、配置静态存储器(SRAM)作为内存、整体结构采用了哈佛结构,可以实现指令流水功能。同时,教学计算机配备了较为丰富的外部接口,如串口、闪存、HDMI、网口等,以及硬件实验必不可少的手拨开关、指示灯,可以完成计算机组成原理的课程实验,也可以满足大多数硬件课程实验的要求。

上图是THINPAD-Cloud教学计算机的外观,与传统的基于74系列逻辑芯片的实验平台相比,基于FPGA的THINPAD-Cloud教学计算机实验平台具有完全的可编程性,学生可以充分发挥自己的创造性,设计出新颖的架构和创新的应用。同时THINPAD-Cloud平台配置的大容量FPGA(100K LEs)使得学生完成较复杂的处理器设计(如带有缓存的流水线CPU)成为可能。

与市面上大多数FPGA开发板不同,THINPAD-Cloud板载了8MB的大容量的静态存储器SRAM,而不是DDR动态存储器。由于SRAM具有访存延迟低、周期固定的特点,这一设计极大降低了内存控制器和CPU访存部分的设计难度,有助于学生实现一个完整的计算机系统。

在外围电路设计上,THINPAD-Cloud提供了32位拨码开关和多个按钮开关,16位LED和两个7段数码管,用于完成基础实验和辅助调试。实验平台还提供了串口、HDMI、以太网、USB等常见的计算机外围接口。其中串口主要用于上位机(即与所连接的计算机)通信,输出调试信息,是实验开发过程中最主要的通信接口。HDMI接口可以外接显示器输出图像,从而实现终端显示、图形界面等。以太网和USB接口供学生自由开发,扩展网络通信、键盘鼠标支持、U盘读写等功能。如果学生完成图形显示和键盘等扩展功能后,整个平台就拥有了自己的输入输出功能,可以作为独立的计算机系统运行,实验成果的可展示性得到很大的提升。

此外,THINPAD-Cloud 还板载了控制模块,集设计文件写入FPGA、串口转换、SRAM读写和Flash读写等功能于一体。平台只需连接一根USB线到开发计算机,免去了外接JTAG下载线和USB转串口线的不便。这些功能支持Windows、MAC和Linux三大主流操作系统,将实验平台连接到装有这些操作系统的计算机后无须安装其他专用程序就可以使用,为实验环境准备带来方便。实验平台内置的SRAM、Flash读写工具,可以帮助实验者快速地把软件程序加载进存储器中,避免通过串口加载的长时间等待,也可以读取存储器内容,帮助对存储器相关实验进行检查。

THINPAD-Cloud实验平台还实现了基于互联网的远程实验功能,实验用户可通过互联网访问远程实验平台,获得和本地实验完全一样的效果,极大地提高了通过该平台进行硬件实验教学的可用性。

实验平台结构

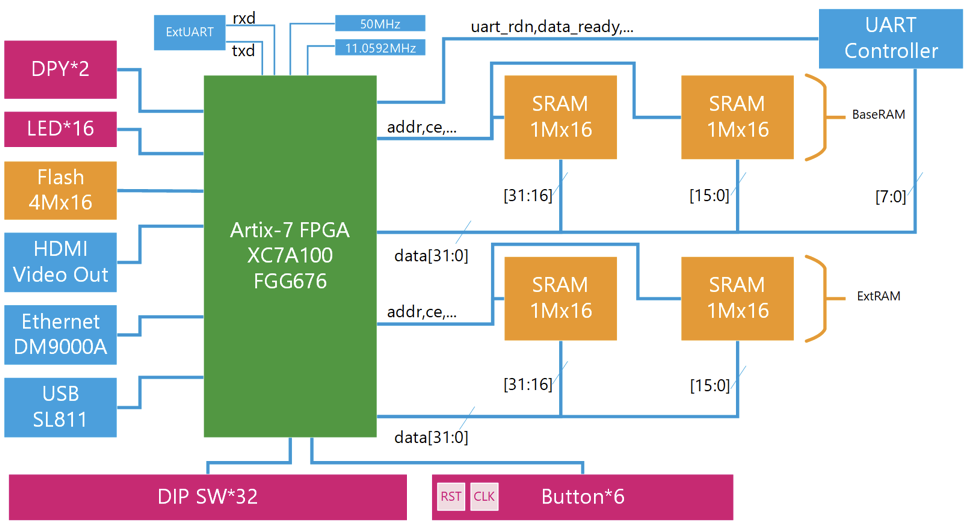

实验平台以一片Xilinx公司的 Artix-7系列FPGA为核心,其型号为 XC7A100TFGG676。它具有101440个逻辑单元(LE),与计算机组成原理相关的大多数实验都可以在其上完成。较大的逻辑容量使学生不但可以在上面实现一个常规的支持指令流水的CPU,还可以扩展实现更高级的功能(如缓存)。

上图是实验平台硬件组成及结构。实验平台上配置了SRAM和Flash闪存两类存储芯片,作为计算机系统的存储器使用。其中SRAM由四片 1 M× 16 位的芯片组成, 每两片组织为一个独立单元,分别称为BaseRAM和ExtRAM,每个单元的容量都是 1 M × 32 位。两个单元的地址、数据和控制信号分开连接到 FPGA。这种内存模式对实现指令流水的计算机架构比较合适,可以将指令和数据存储在两个不同的存储空间,实现在一个机器周期中同时访问指令和数据,以避免指令流水带来的结构冲突。 当然,用户也可以将两个存储器单元逻辑上合并为一个 8 MB 的内存单元使用,以运行一些要求内存容量比较高的程序,如完成嵌入式操作系统等的实验。

实验平台配置的非易失性存储器是一片8 MB容量,16位数据位宽的 NOR 闪存。 实验者可以使用它来实现文件系统,也可以用来存储操作系统镜像文件。在调试硬件逻辑时,每次启动可以从闪存直接加载软件。由于从闪存载入镜像文件比串口快,可极大地节省调试硬件逻辑的时间。

实验平台配置有一个串口控制器,支持简单的异步串行接口通信功能。串口控制器与FPGA之间是并行的接口,包括8位数据信号线和几根控制信号线。其中数据信号与BaseRAM的数据线共享,相当于引入了共享总线的概念,要求学生设计的处理器在访问串口时需要处理总线冲突问题。

为了硬件实验调试的需要,实验平台提供了简单的 I/O 组件,包括有32 位 DIP 开关、2个带硬件去抖动的按键、4个无去抖动的按键直接连接到 FPGA 作为用户输入。其中硬件去抖动按钮主要用作单步时钟输入和复位信号输入,其余按钮开关可以在小实验中用作数据、指令输入。板上还有两个 7 段式数码管,和 16 个 LED 灯连接到 FPGA。这些输出信号,一方面可在实验中用于显示结果,另一方面也可以作为调试输出,连接到内部逻辑中,观察信号状态。

实验平台上为FPGA提供两个时钟输入,频率分别是50MHz和11.0592MHz。其中50MHz可以作为CPU设计的主时钟,也可以连接到FPGA内部的时钟管理单元,生成所需的任意频率的时钟。11.0592MHz主要用于串口通信,该时钟信号经过整数倍分频后可以直接得到标准的串口的波特率数值。

此外,实验平台上还提供了丰富的外部接口资源,包括DVI 并串编码芯片,它可将图像数据经由HDMI接口输出到显示器上;100M以太网网卡芯片,可提供网络连接能力;还有USB接口芯片,可支持键盘、鼠标、U盘等常见计算机外设。

远程实验平台使用方法

THINPAD-Cloud实验平台支持远程实验功能。实验平台已经和学校的实名认证系统连接在一起。学生使用自己的学号(用户名)和密码就可以通过浏览器登录到远程实验平台,成功连接到远程实验板,并在板上完成实验。

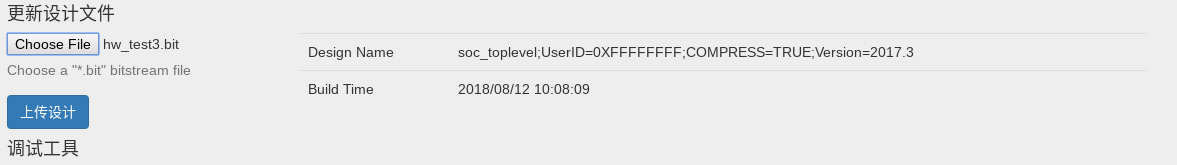

设计文件上传

打开远程实验平台网站并登录后,网页上会列出可用的实验板及描述信息,学生根据需要选择实验板并上传设计文件。

这里的设计文件必须是Vivado工具生成的.bit格式的比特流文件。如果选择文件格式正确,页面会显示文件信息,"上传并开始"按钮也会变为可点击的。文件信息中包含Vivado顶层模块名称和编译时间等,用户可据此判断是否选择了正确版本的文件。

上图为远程实验板选择和上传设计文件界面。点击"上传并开始"按钮,系统将分配实验板,并将设计文件写入实验板上的FPGA中。随后浏览器自动跳转到"工作区域"。

实验平台的基本操作

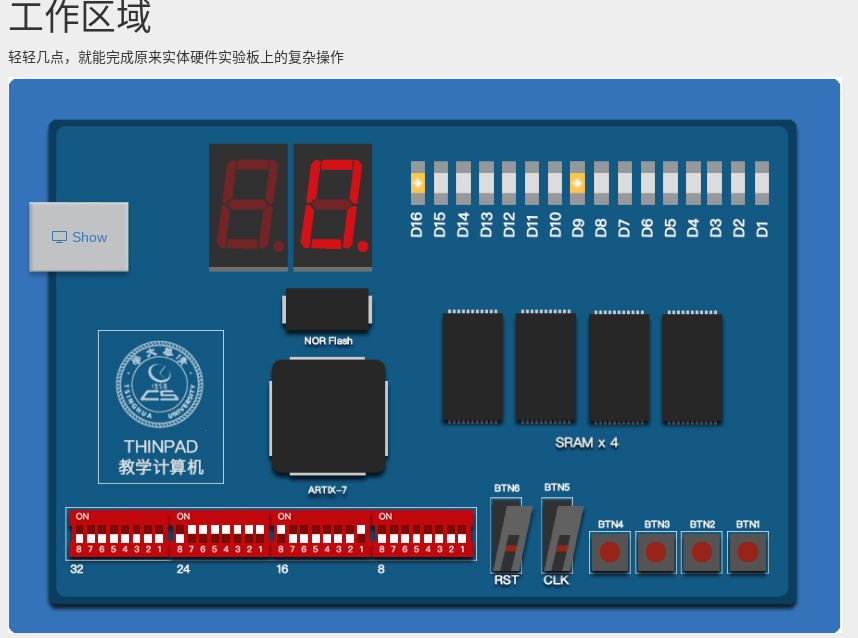

进入"工作区域"后,可以看到一个接近真实实验板外观的操作界面,如下图所示。界面上的按钮和开关均可以点击,效果等同于直接操作真实的实验板。界面上的数码管和LED会显示为点亮和熄灭效果,其状态与真实板上的显示一致。

进入"工作区域"后,可以看到一个接近真实实验板外观的操作界面,如下图所示。界面上的按钮和开关均可以点击,效果等同于直接操作真实的实验板。界面上的数码管和LED会显示为点亮和熄灭效果,其状态与真实板上的显示一致。

操作界面左上方对应实验板HDMI连接器的位置,有一个按钮,点击后会弹出虚拟显示器窗口。在完成图像显示相关实验时,实验者可以使用该功能远程查看实验板输出的图像。

与本地实验类似,远程实验也需要通过串口和实验平台进行交互、实验调试过程中经常需要更新设计文件、也需要完成对存储器系统的读写操作。这些功能在远程平台都可以方便地实现。

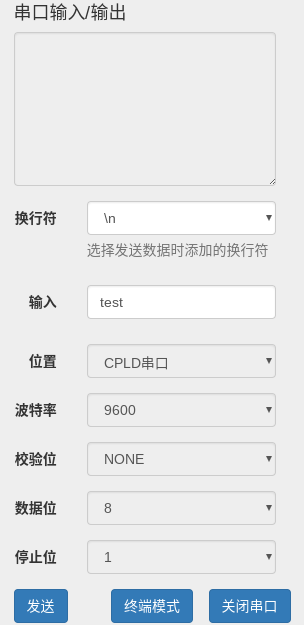

1. 串口访问

操作界面的右侧是串口控制区域。顶部文本框显示平台从串口接收到的数据(即FPGA发送的数据)。其下有几个输入控件,功能依次为:

a. 换行选择:设置使用输入框发送数据时,是否自动在数据后添加换行符

b. 发送数据:待发送数据的输入框,用户输入文本数据,按回车键发送

c. 串口选择:选择CPLD串口或直连串口

d. 波特率:设置通信用的串口波特率

e. 校验位:设置校验位为奇校验、偶校验或无校验位

f. 数据位:设置数据位长度为6、7、8位,通常设为8

g.  停止位:设置停止位长度为1或者2位,通常设为1

停止位:设置停止位长度为1或者2位,通常设为1

上述串口参数需要根据实验者的设计或者实验要求来设置,且仅在串口关闭状态下可以更改。

输入控件下方是控制按钮。点击"打开串口"和"关闭串口"按钮可以打开、关闭串口。点"发送"按钮可以将发送数据输入框的内容从串口发送出去,其效果与输入框中按回车一样。点击"终端模式"按钮后,程序将全屏显示串口输入输出内容,并按照UNIX终端规范来解释特殊转义字符。进入终端模式后,鼠标点击左上角按钮即可退出。

在"工作区域"的更新设计文件面板上,用户可以替换当前运行的设计文件。文件格式要求和操作方法与首次上传设计文件时相同。

2. 存储器读写

与本地实验板类似,远程实验平台也支持读写板上的SRAM和Flash存储器。其界面如下所示。需要指出的是,读写Flash和RAM时,为了避免信号电平冲突,系统会清除实验FPGA中的用户设计,并在读写完成后自动重新载入。

上图为远程实验的存储器读写界面。

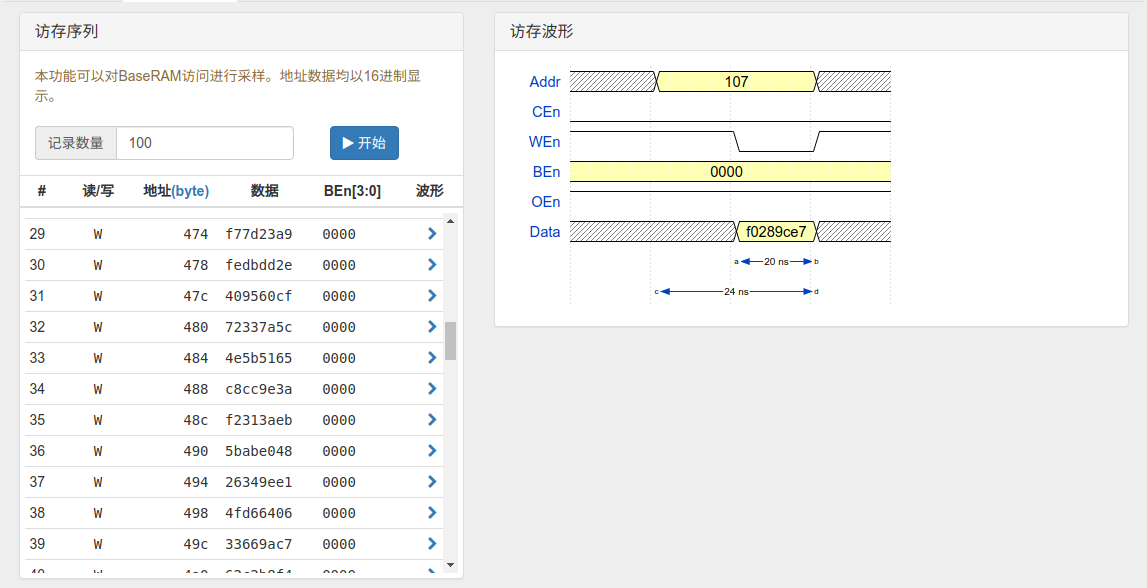

与本地实验不同的是,远程实验平台增加了一个功能,能够记录程序运行过程中,对SRAM访问时的地址序列。这给实验者提供了一个十分实用的调试手段。该功能可以记录FPGA对BaseSRAM的读写操作,记录内容包括地址、数据及控制信号的波形。通过检查访存序列,学生可以更直观地了解SRAM的操作方法,更容易地调试访存相关的错误。

上图为记录SRAM访问地址序列的设置和操作界面。访存序列记录功能使用方法非常简单。在上图中设置需要设定记录访存的次数,然后点击开始按钮,系统就开始在后台记录访存了。此时实验者的FPGA设计如果按照时序要求读写了BaseSRAM芯片,读写的地址、数据等信息就会被记录下来。当记录数量达到设定值时,系统停止记录,并将结果显示在页面上。

实验者可在列表中浏览系统记录下的访存序列,点击每条记录右边的按钮,可以查看该访存的波形。在解决时序问题时,实验者可以参考该波形上的时间标注。由于采样率的限制,时间标注的误差为4ns。