实验三 简单组合逻辑电路实验

实验目的

- 深入理解用小规模数字集成电路组成组合逻辑电路的分析与设计方法。

- 通过全加运算电路和减法运算电路的设计,熟悉“补码”的概念以及用“补码”实现减法运算的方法。

实验内容

- 全加器:设计一个两位全加运算电路,实现 C=A+B 的运算(A 和 B 分别为 0~3 的数),并用数码管显示运算结果,进位信息用发光二极管指示。。

- 补码结果减法器:设计一个两位减法运算电路,当 A ≥ B 时,数码管显示出相减的差值;当 A < B 时,数码管显示出用补码表示的差值,借位信息用发光二极管指示。(选做)

- 原码结果减法器;设计一个两位减法运算电路,当 A ≥ B 时显示所得的差;当 A < B 时显示出负号及用原码表示的差值,符号位用发光二极管指示。(选做)

注意

本实验中默认A和B均为非负整数

根据所使用的芯片不同有不同的设计电路,只要功能正确即可

预习要求

- 复习组合逻辑电路的分析与设计方法的有关内容,熟悉实验所用门电路的引脚图;

- 按实验任务要求设计电路,画出完整的逻辑电路图,说明设计过程与方法。

- 拟定实验步骤,设计必要的记录表格。

关于实验过程和预习

本实验的电路较为复杂,请同学们在进行实验前做好充足的预习准备。提高要求 3 的电路搭建大概需要 15 分钟的时间。你可能还需要额外的时间进行调试,时间仅供参考。

实验步骤

2 位全加器

- 首先设计出 1 位全加器,使用真值表将通过逻辑化简生成可以对应到基本门电路的电路图;

- 使用两个 1 位全加器通过串行进位组合成 2 位全加器,画出完整 2 位全加器电路图;

- 按照电路图使用芯片搭建出电路图,调试通过。

补码结果减法器

- 使用补码来表示负数,减法就变成了加法, 补码 = 反码 + 1 ,将 B 取补码(B 逐位取反,全加器进位输入取反),在全加器的电路图基础上画出电路图;

- 按照电路图使用芯片搭建出电路图,调试通过。

原码结果减法器

- 设计一个补码转原码电路,加在补码结果减法器的输出后面,将补码结果转换成原码结果;

- 按照电路图使用芯片搭建出电路图,调试通过。

Tips

可以将上面 3 中运算器做成一个电路,通过开关选择此时是哪种运算器在工作。

建议的设计思路

- 绘制功能的真值表

- 使用卡诺图方法进行化简,获得只使用与和或的逻辑

- 将表达式换为使用与非和异或的逻辑

- 绘制接线图,使用 74LS00 和 74LS86 进行电路搭建

参考设计,如果没有思路可以参考,请不要无脑抄电路图

- 1 位全加器

1位全加器的真值表如下:

通过整理后仅使用与非逻辑和异或逻辑,得到 Fn 和 Cn 的逻辑表达式为:

$$ F_n = A_n \oplus B_n \oplus C_{n-1} \ $$

$$ C_n = \overline {\overline{A_n \cdot B_n} \cdot \overline{C_{n-1} \cdot (A_n \oplus B_n)}} $$

对应的电路图如下:

实际接线后的电路如下:

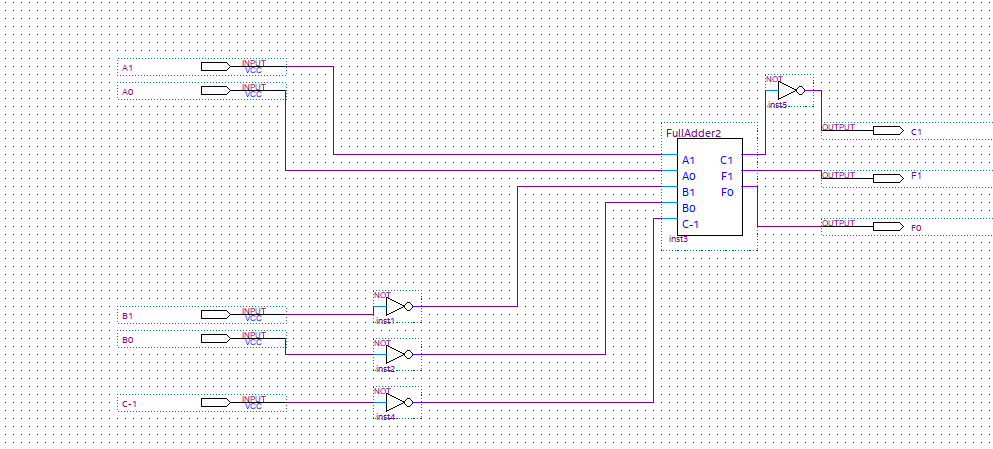

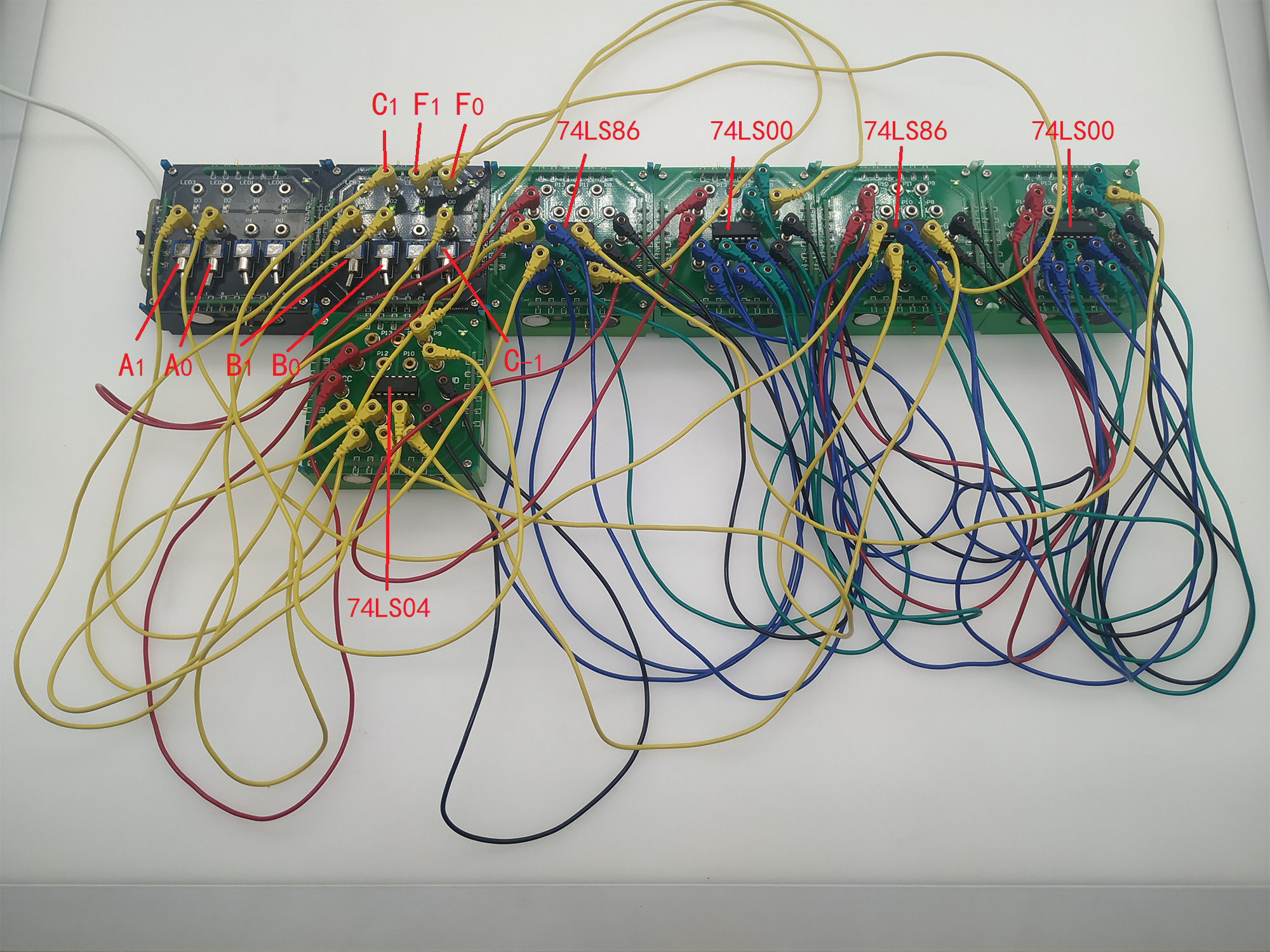

- 2位全加器

使用2个1位全加器串联,低位的全加器的进位输出接到高位全加器的进位输入,构成2位全加器:

对应的电路图如下:

实际接线后的电路如下:

建议

本电路图中为了展示方便使用了两片74LS86,在实际中可以只使用一片就够了。

- 补码结果减法器

基于2位全加器,将B取补码(B逐位取反,全加器进位输入取反),构成补码结果减法器:

对应的电路图如下:

实际接线后的电路如下:

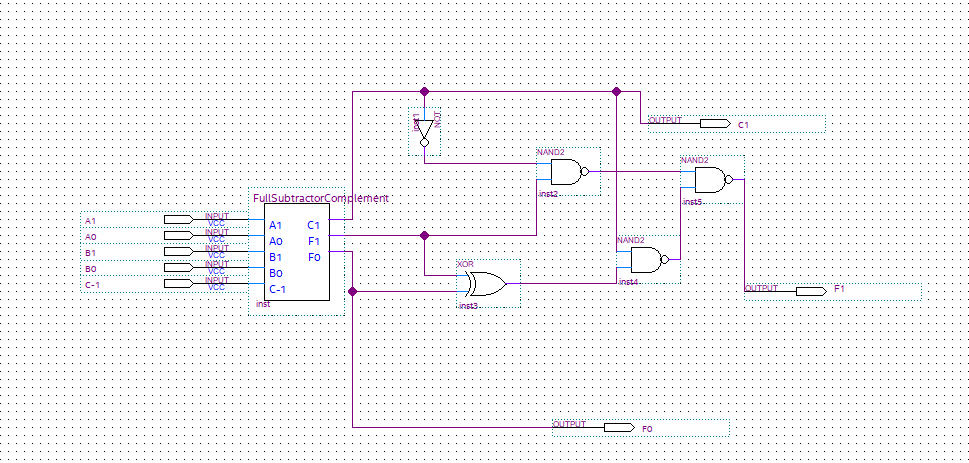

- 原码结果减法器

基于补码结果减法器,将结果的补码转换成原码,补码转原码的真值表如下:

对应的电路图如下:

实际接线后的电路如下:

网图,如有盗用,请联系我们。

致谢!

本部分设计完全使用了高焕昂同学的实验报告,在此表示感谢。

注意

芯片摆放尽量按逻辑产生先后顺序,根据信号传递的方向(从输入到输出)来安排,方便接线以及检查;

用不同颜色的导线来接线,例如红色线用于接电源、黑色线用于接地等等,这样做可以帮助排查接线错误;

可将芯片引脚编号标注在电路图上,可以提高连线速度,也可以帮助检查错误;

带译码器的数码管,不用的高位应该置零(接地)不能悬空,否则显示不正确;

接插电路时要认真检查,不要漏接,尤其要注意电源线和地线不要漏接;不要窝腿造成漏接;

不许带电操作,接插线及更换元件时要关电源。

一些调试技巧

通常采用先分调后联调的调试方法,按功能将电路分解为若干个单元,分别将各单元调试好,再按顺序将各单元逐级连接,扩大调试范围,最后完成整个电路或系统的调试;

检查故障时,首先检查芯片的VCC和GND,测量点应是集成电路的管脚处;

按逻辑产生先后顺序查错,从逻辑发起端开始,逐步找到错误;

可将芯片引脚编号标注在电路图上,可以提高连线速度,也便于检查故障。

实验报告要求

- 整理实验数据。

- 总结加法运算电路、减法运算电路的设计方法。

- 在实验中所遇到的故障和问题以及解决方法。

- 设计一个四位二进制除法运算电路,A 为被除数,B 为除数,C 为商数,D 为余数,画出具体逻辑图或框图,并描述其工作原理。