ILA

进阶功能

本章节属于拓展功能,其主要目的是给大家一个做一个简单的进阶参考。进阶实验的目的是锻炼大家的自学能力。因此对本章节内容的答疑可能不会被接受。特此声明。

在一些较为复杂的硬件设计项目中,由于仿真较慢,可能会遇到在无法仿真的情况下出现错误需要调试的情况。这时 ILA(Integrated Logic Analyzer, 集成逻辑分析仪)在线调试自己的设计,抓取在实际运行时部分信号的波形。

在本节中,我们将介绍在项目中例化使用 ILA 的方法。

引入 IP 核

-

在 IP 目录中找到

ILA (Integrated Logic Analyzer), 双击开始配置 IP 核。

-

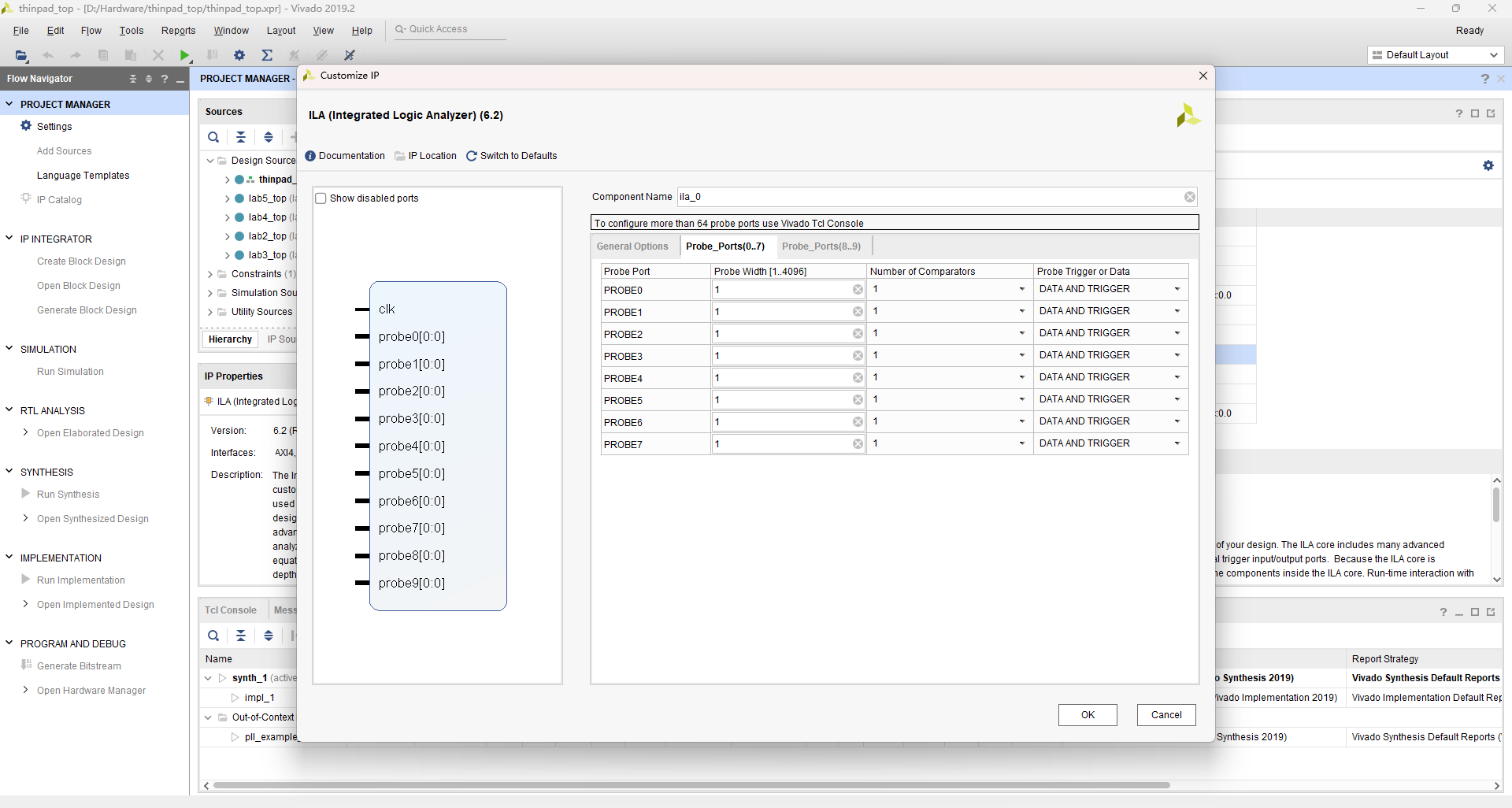

进行 ILA 的配置

- Number Of Probes: 需要抓取的信号数量。

- Sample Depth: 抓取深度,即抓取多少个周期的信号。

- Number Of Comparators: 每个信号的比较逻辑门数量。这个我们会在后面讲触发的时候具体解释。

剩下的配置不要更改。

注意在 GUI 界面上配置的 ILA 最多只能够抓取 64 个信号。如要抓取更多信号,请自行学习 tcl 命令生成 ILA。但一般来讲 64 个信号已经相当够用了。

同时也请注意,ILA 使用 BRAM 存储抓取的信号。由于 BRAM 资源有限,请不要设置过大的 depth,一般 1024 已经足够。

-

在后面的几页中,每页有若干信号,用来配置 ILA 每个探针的宽度,即要抓取的信号的位宽。

一般我们会在设计中先例化 ILA 进行接线,再来到这里配置信号宽度。(注意项目中的 ip 核可以双击打开进行配置,但不能改名字)

信号和使用

ILA 的信号相当简单:

- clk:时钟信号,输入,确定信号抓取的频率,一般与整个设计的时钟相同。

- probe(x):输入,你要抓取的第 x 个信号

然而在使用 ILA 时,要确保该信号不会在综合或布线时被优化掉,因此需要在需要抓取的信号前加入 (* MARK_DEBUG = "TRUE" *)。一个例子如下:

(* MARK_DEBUG = "TRUE" *) wire[3:0] signal_a;

(* MARK_DEBUG = "TRUE" *) reg[3:0] signal_b;

ila_0 ila(

.clk(clk_i),

.probe0(signal_a),

.probe1(signal_b)

);

注意,在 module 中定义的 input, output, inout 信号不能抓取。

关于在云平台上 ILA 的使用方法,以及触发,我们将在后面的例子中进行说明。

更详细的说明和使用方法可以去 Xilinx 官方文档网站查看: ILA 文档