运算部件

进阶功能

本章节属于拓展功能,其主要目的是给大家一个做一个简单的进阶参考。进阶实验的目的是锻炼大家的自学能力。因此对本章节内容的答疑可能不会被接受。特此声明。

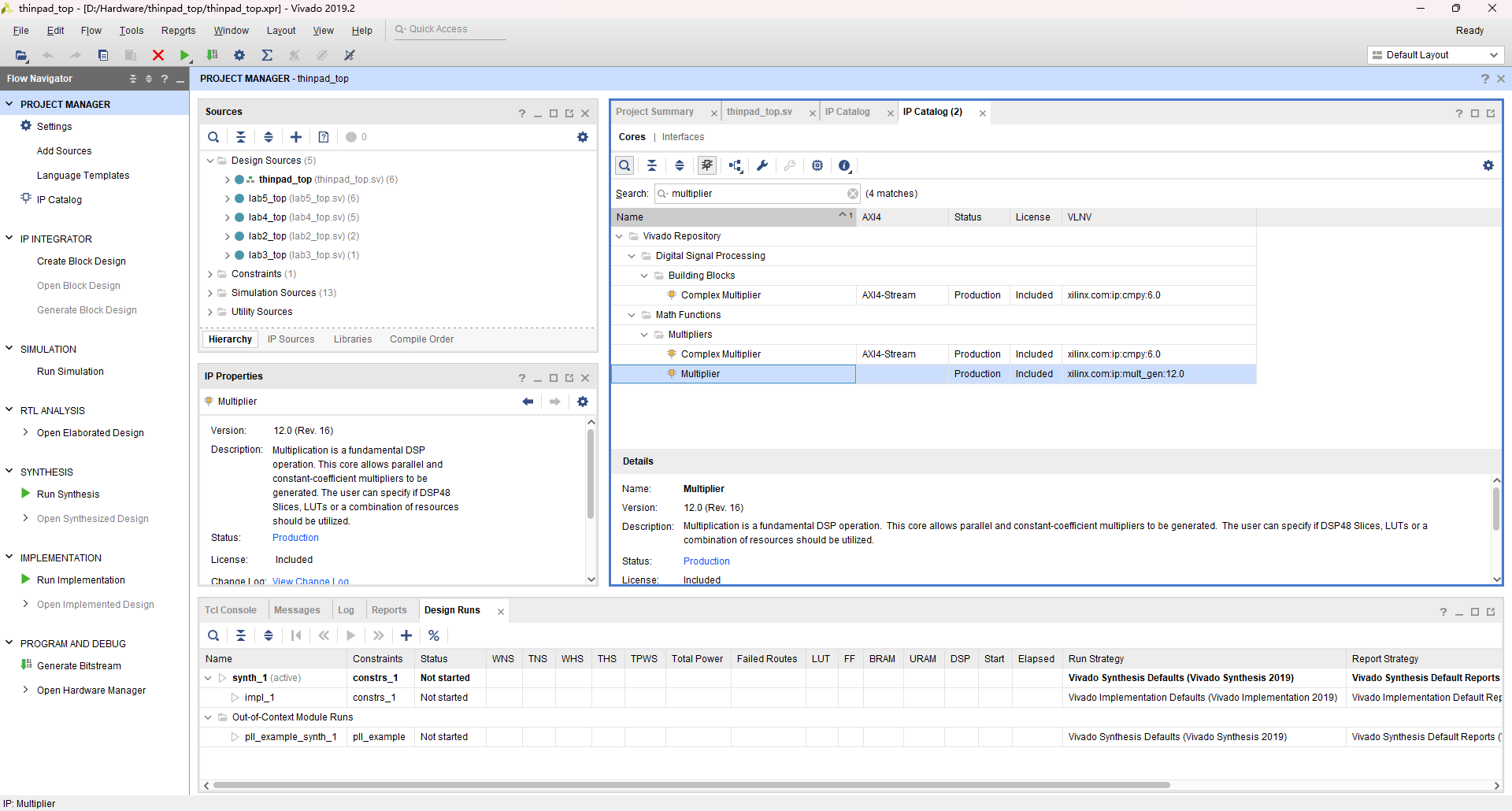

引入 IP 核 - 乘法器

-

在 IP 目录中找到

Multiplier, 双击开始配置 IP 核。

-

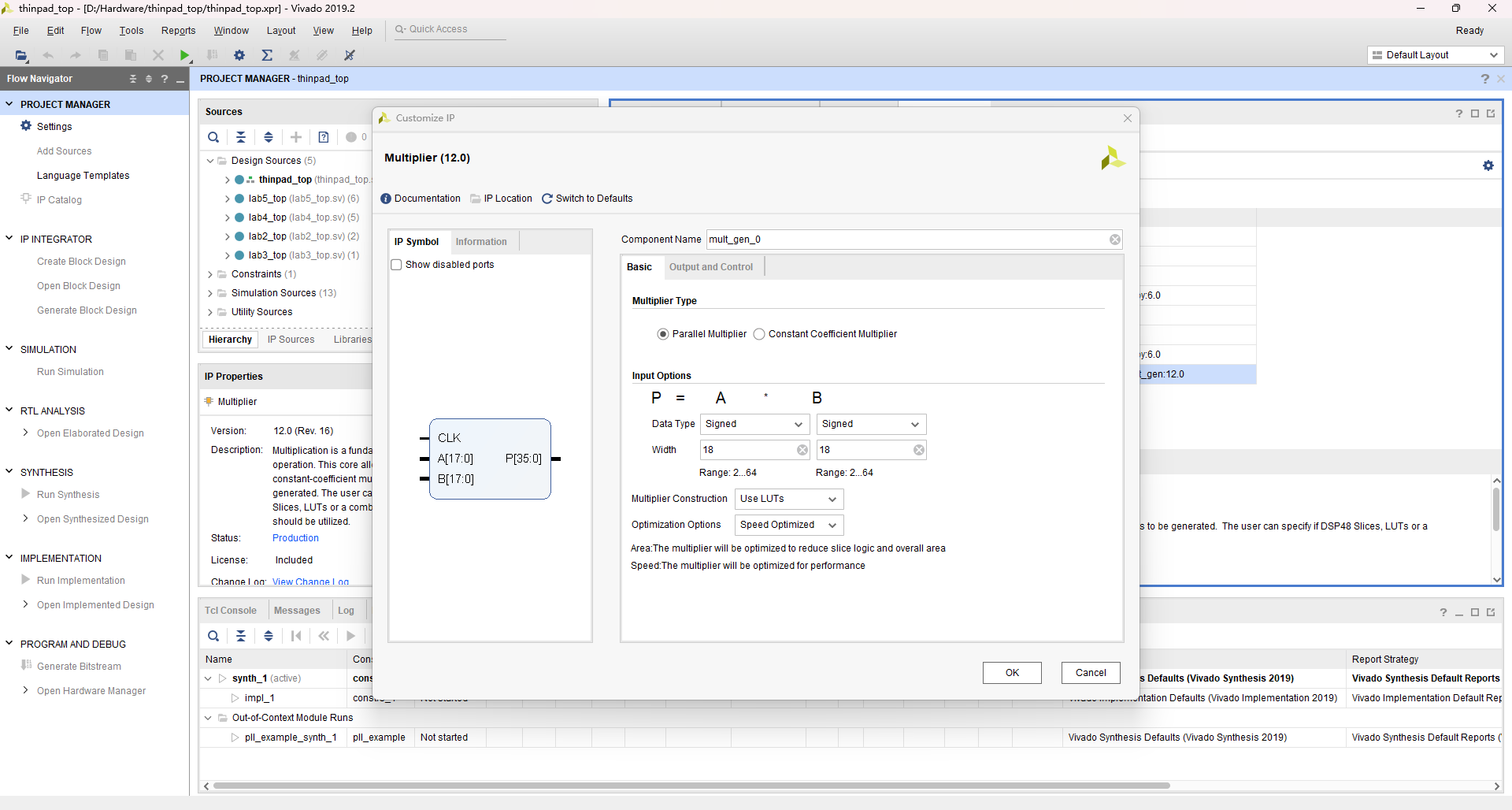

配置两个乘数的类型(有符号/无符号),以及位数。

剩下的配置不需要更改。

-

在第二页配置乘法器的延迟和输出。

一般输出配置不需要更改。

Pipeline Stages即为流水线级数,右侧会显示最优级数,在此配置下生成的乘法器占用资源最少。乘法器的内部是流水的。一般配置为最优级数,若更少,则乘法器会占用大量资源,增加时序违约的可能性。关于流水线级数

这里的流水线级数可以设置为 0,即可以综合为组合逻辑。设置级数为 1,则为延迟一拍,下一个周期才能够获得结果。更多的级数以此类推。

Synchronous Clear即为同步复位信号,该复位信号将清空乘法器流水线。

乘法器信号和时序

CLK: 时钟信号A, B: 输入,两个乘数P: 输出,乘积SCLR: 同步复位信号

下面假定 Pipeline Stages 为 3,一个乘法器时序如下:

注意到每周期输出的结果都是 3 个周期之前的乘积,即内部使用一个 3 个阶段的流水线来计算乘法。

同步复位会在 CLK 上升沿到来且 SCLR 为 1 时清空乘法器内流水线,即从当前周期开始连着 3 个周期输出 0,之后恢复。

更详细的说明和使用方法可以去 Xilinx 官方文档网站查看:乘法器文档

AXI Stream 握手协议

请先回顾 自研总线的设计 一节,然后再来看本节的握手协议。

AXI Stream 总线只有以下几个信号:

aclk: 时钟信号tdata: 数据tvalid: 高表示 master 想要发送请求tready: 高表示 slave 完成请求处理

同学们可以与自研总线以及 Wishbone 总线中的信号对比,理解这几个信号的意义。

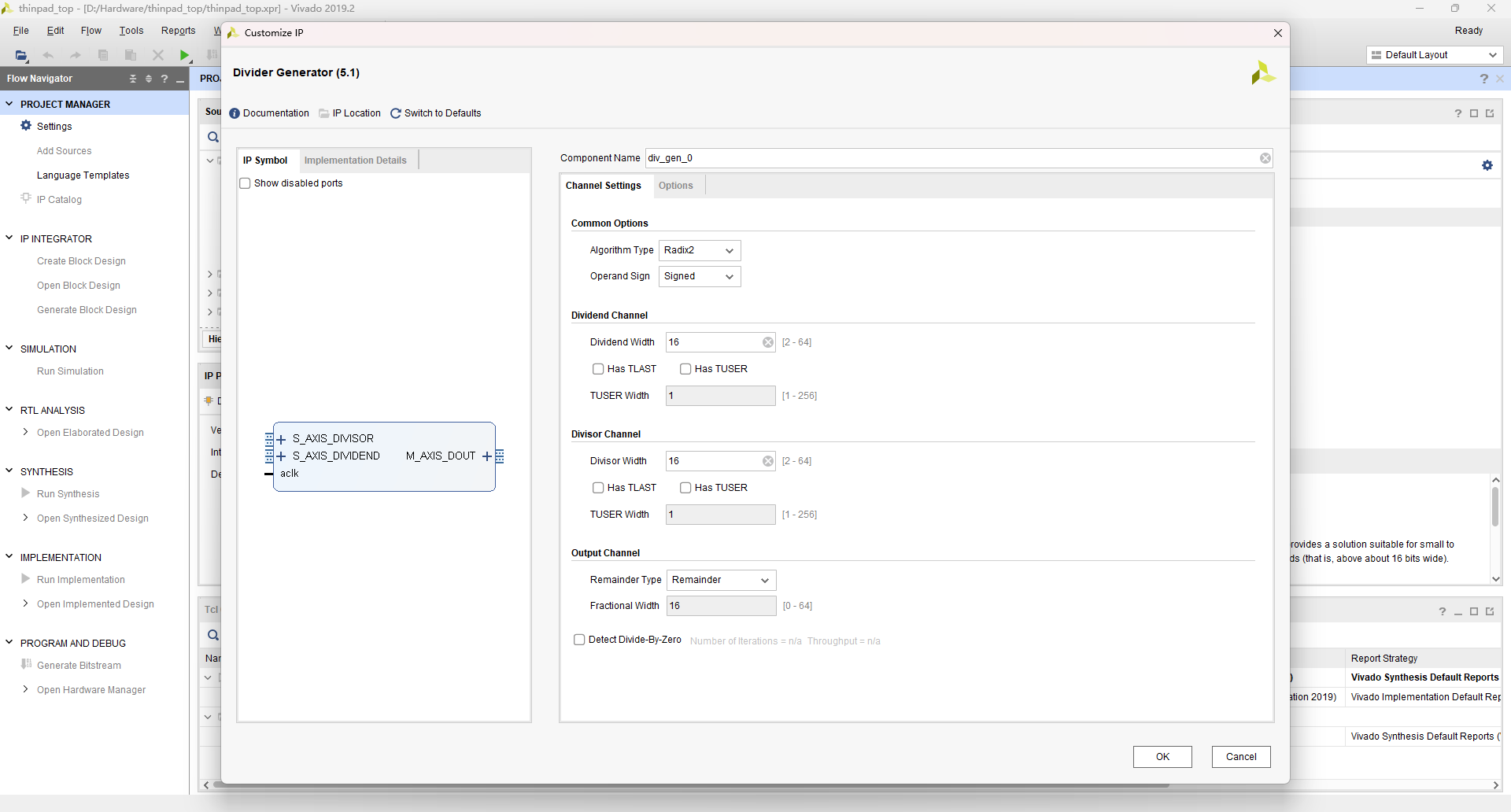

引入 IP 核 - 除法器

-

在 IP 目录中找到

Divider Generator, 双击开始配置 IP 核。

-

Operand Sign: 配置被除数和除数是否带有符号位Dividend Channel中配置被除数的位数,其余设置不要修改。Divisor Channel中配置除数的位数,其余设置不要修改。在

Output Channel中选择Remainder模式,这样输出的是商和余数。记除数和被除数中位数较多者的位数为 x ,则输出

tdata有 2x 位, 高 x 位为商,低 x 位为余数。选择

Detect Divide-by-Zero, 这样在除 0 时, 输出端的tuser会输出 1。

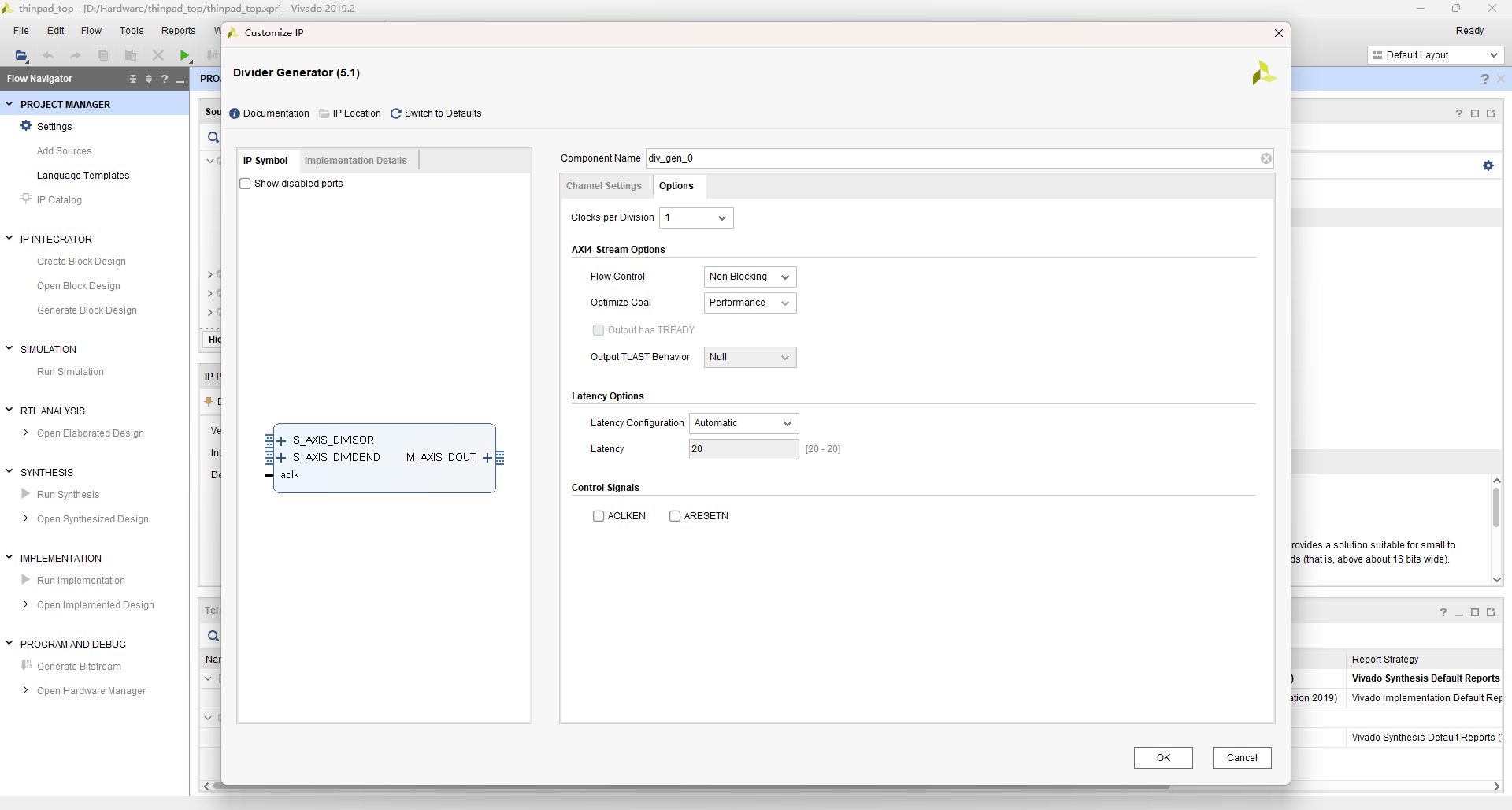

-

第二页中选择工作模式为阻塞还是非阻塞。非阻塞的模式与乘法器的工作模式类似。如为阻塞模式,一般要选择

output has tready,否则 valid 信号将在输出结果后拉低,使结果只有一个周期有效。选择

ARESETN则会向除法器中加入 0 使能的复位信号。

更详细的说明和使用方法可以去 Xilinx 官方文档网站查看:除法器文档

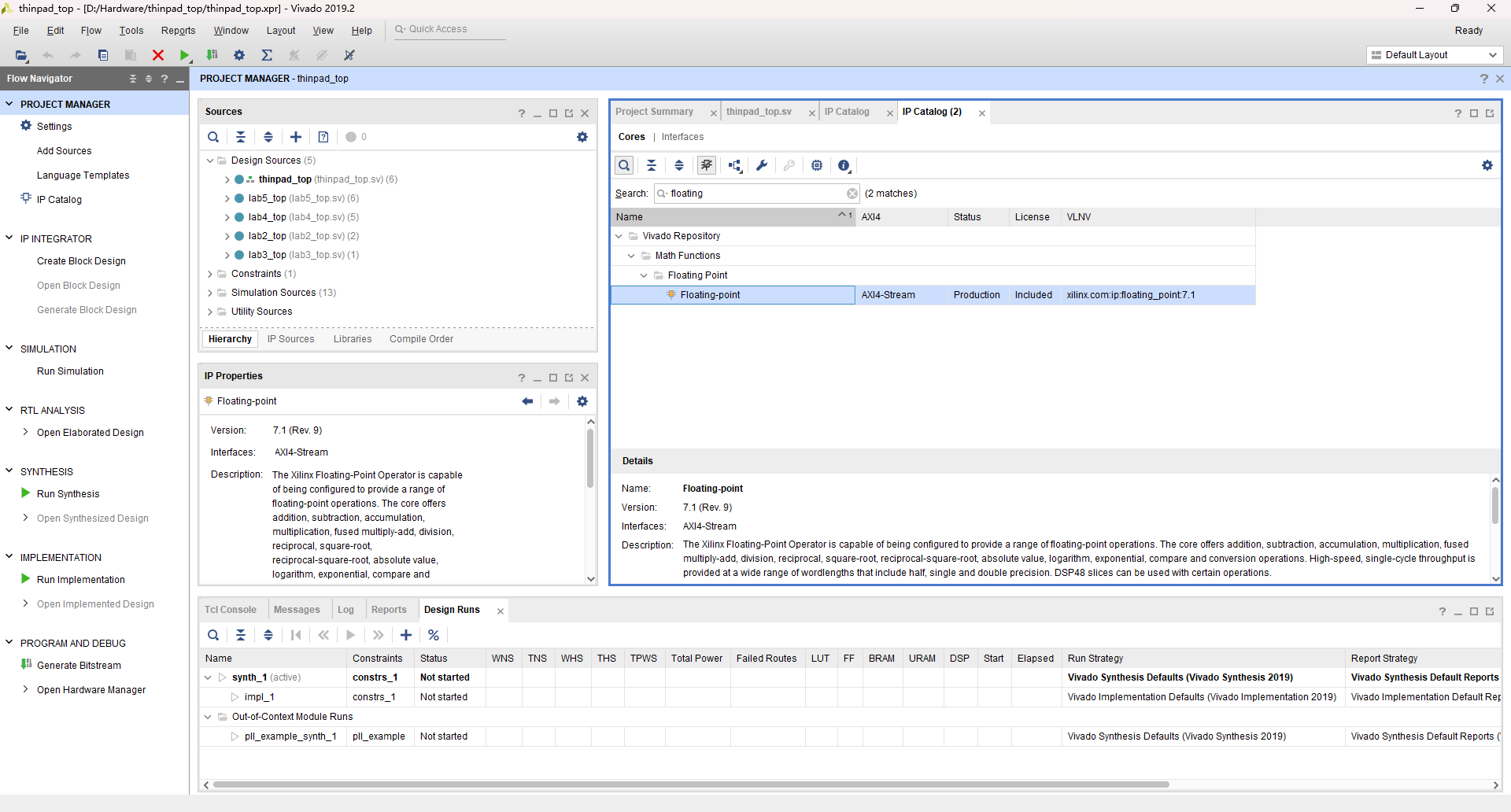

引入 IP 核 - 浮点运算器

-

在 IP 目录中找到

floating-point, 双击开始配置 IP 核。

-

在之后的几页中可以配置操作数精度,运算类型,以及工作在阻塞模式还是非阻塞模式。同时还会有是否输出上溢、下溢等标志,以及是否使用复位信号等等。在此不多赘述。

-

更详细的说明和使用方法可以去 Xilinx 官方文档网站查看:浮点运算器文档