概览

实验概述

本学期共有 6 个实验,包含 5 个小实验(所有学生独立完成)和 1 个大实验(选做,不超过 3 人组队完成):

实验 1:监控程序,熟悉 RISC-V 汇编语言编程

实验 2:ALU 和寄存器堆实验,熟悉二者的实现方法,适应结构化的硬件设计思维

实验 3:SRAM 控制器实验,理解 Wishbone 总线的基本概念,熟悉 SRAM 时序

实验 4:内存串口实验,熟悉 Wishbone 总线 Master 的实现,理解总线的设计

实验 5:处理器实验,利用前序实验(主要是实验 2 和实验 4)的知识,实现简单的处理器设计

大实验(选做):综合计算机系统实验

本学期实验不要求所有同学都参与设计和实现综合计算机系统,即大实验不是必须的内容。除了最后的大实验之外,前面的 5 个必做实验要求所有同学独立完成。大实验分组开展,1~3 位同学为一组,鼓励有兴趣的同学组队完成。

另外,对数字逻辑和硬件编程不太熟悉的同学可以通过计数器实验(选做实验 0)了解和熟悉相关内容。

选做实验 0:计数器实验,熟悉 Vivado 开发软件和工程模板,编写简单的时序逻辑和组合逻辑

实验平台概述

计算机组成原理的实验最终目的是设计并实现一个能够完成基本功能的处理器,并驱动内存以及串口来运行一个简化的操作系统("监控程序 Supervisor")。为了能够和监控程序进行交互,还需要终端程序(Term)与监控程序通过串口进行交互。ThinPad 开发板提供现场可编程门阵列(FPGA),内存,以及串口。实验的工作是编写一个 RISC-V 处理器,将其装载到 FPGA 中。完成之后的处理器将执行监控程序,并与终端程序交互。监控程序保存在内存中。

它们之间的关系如下:

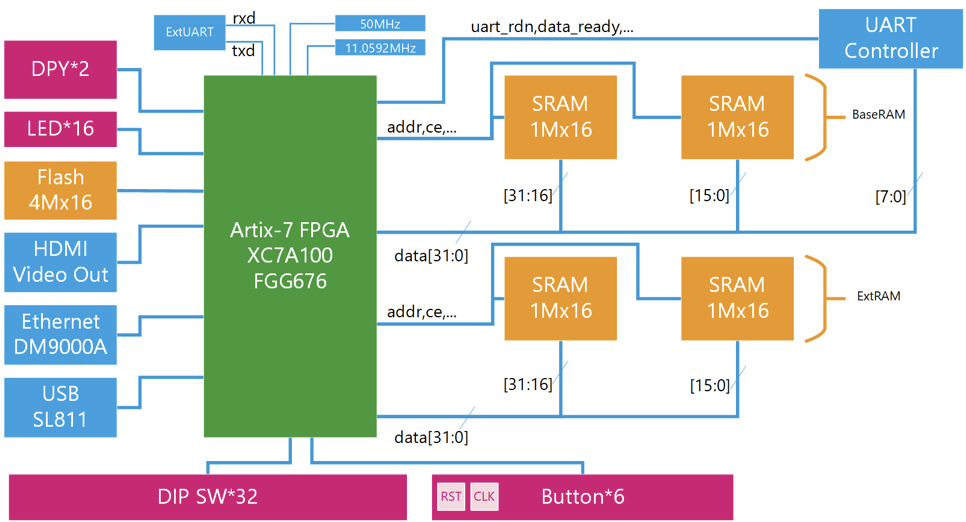

实验平台提供了 FPGA,内存,以及串口硬件,其结构框图如下。实验的目的就是设计一款处理器,将处理器装载在 FPGA 处运行。处理器从内存中读出每一条指令,执行每一条指令。有一些指令需要读写内存,另外一些指令需要读写串口。如果进行串口读写的话,将与终端程序进行交互。

完成计算机组成原理实验的要点是:(1)掌握 RISC-V 的指令系统与指令格式;(2)掌握组合逻辑和时序逻辑的设计方法,重点是状态机的设计;(3)掌握 Wishbone 总线和 SRAM(静态内存)的驱动方法。

关于第一点,需要准备两件事情:(1)熟悉 RISC-V 的指令系统,熟悉 RISC-V 的汇编程序;(2)熟悉 RISC-V 的指令格式。必须要详细阅读 RISC-V 的指令手册,阅读监控程序和终端程序的源代码。监控程序类似于一个简化的操作系统,能够完成简单的接收输入命令,执行命令并输出结果的流程。监控程序也作为最后的大实验的检验标准,即大实验需要正确运行监控程序。

关于第二点,掌握组合逻辑和时序逻辑的设计方法,这是同学们在数字逻辑课程中学过的内容。有一部分同学对此不是特别熟悉,或者实验技能还没有达标,建议在做实验之前复习一下数字逻辑课程的内容。有一部分同学没有系统的学习过数字逻辑课程,需要自学相关的内容之后再选《计算机组成原理》课程。

关于第三点的内容,主要是掌握 SRAM 的硬件行为特征,特别是其时序特征和以及对应信号的使用方法。在本实验指导书中会详细介绍实验平台 SRAM 的时序特征。同学们在开始相应实验之前需要仔细体会器件的工作原理和工作时序。

另外,为了能够进行硬件的实验,掌握硬件描述语言(HDL)是必须的。在语言的选择上,本课程推荐使用 SystemVerilog 语言。但是同学们也可以根据自己的喜好,选择各类高层次 HDL 进行设计,包括但不限于基于 Scala 语言的 SpinalHDL、Chisel,以及基于 Python 语言的 Migen 等。本实验指导书以 Verilog / SystemVerilog 举例。

硬件设计

无论选择哪种高层次 HDL 语言,其描述的依然是实际的硬件,如寄存器、逻辑门、连线等。因此,即使选用上述基于 Python 等软件语言的 HDL 框架,仍然需要了解并熟悉硬件设计的思维模式。

使用高层次 HDL

包括 Vivado 在内的 EDA 软件,仅能支持 Verilog 等“传统 HDL”的综合、仿真。因此,其他语言的设计一般需要转换为 Verilog 语言才能够在 Vivado 中使用。请参考对应语言的使用手册来了解如何转化为 Verilog 或者 VHDL 语言。

本手册会将会介绍 SystemVerilog 语言,特别是该语言可以综合的部分。在展开硬件实验之前必须要在一定程度上掌握 SystemVerilog 语言。如果想使用其他的语言,同学们也可以从互联网上搜寻相关的材料和例子。

模拟环境,监控程序,终端程序

课程组提供能够执行监控程序的模拟环境。模拟环境基于 QEMU,模拟了 RISC-V 的指令功能以及基于 RISC-V 的系统,可以运行监控程序。终端程序也可以与模拟环境中的监控程序进行交互。模拟环境模拟了真实的硬件执行情况,可作为大实验正确性的对比。

如果将监控程序运行在模拟环境中,则模拟环境替代了物理实验平台,监控程序保存在模拟内存中,模拟的 RISC-V 处理器执行监控程序。QEMU 模拟的 RISC-V 处理器包括了完整的指令集,自然也包括了在实验中需要实现的指令。模拟的处理器会模拟监控程序的每一条指令的执行,并依据指令的功能去驱动模拟的串口,或者完成对模拟内存的读写。模拟串口的行为和实际串口是一致的,也可以和终端程序进行交互。实验最终设计实现的处理器执行监控程序应当获得相同的效果。

实验相关的参考信息

指令集手册

RISC-V 官方指令集手册:

https://riscv.org/technical/specifications/

以下是中文简化版:

http://riscvbook.com/chinese/RISC-V-Reader-Chinese-v2p1.pdf

中文简化版的内容会有不准确的地方,在阅读的时候需要注意,很容易可以看出来。官方指令集手册是正确的。同学们在开始实验 5 和大实验之前,务必完整阅读中文简化版的第一章,第二章和第三章的内容,对 RISC-V 的总体指令情况有大致的了解。其它各章为扩展指令,仅做参考,可在有必要的时候再看。

硬件开发环境

本课程使用的实验芯片是 Xilinx 公司开发的 FPGA 芯片,配合课题组设计的实验开发板,因此必须要使用 Vivado 集成开发环境进行开发。

Vivado 集成开发环境只能在 Windows 或者 Linux 下面运行,不能在 macOS 下面运行。同学们可通过下列方式中获取:

- Vivado 2024.2(Windows+Linux 通用版本,校内服务器,不消耗校园网流量):

- Xilinx 官网下载链接(请手动选择 2024.2 版本):

macOS(x86_64)下面可通过安装虚拟机解决。

由于 Vivado 不支持 aarch64 指令集,在 aarch64 Linux 上无法运行 Vivado。网上有一些在 Apple Silicon Mac 上使用 Rosetta 2 运行 Vivado 的尝试,但不确定是否可以正常工作。

由于 Vivado 的安装文件特别巨大,解压缩之后占用很大的空间,安装 Vivado 需要预留至少 60GB 的可用空间。后面有专门的章节介绍 Vivado 的使用方法,包括如何进行项目开发,如何进行仿真测试。在安装的时候只需要安装 WebPack 版本即可,安装完成之后的安装文件可以删除。另外,实验的硬件环境也仅支持此版本的开发,不支持其它版本,请同学们仅使用该版本开发。

监控程序最新版,硬件顶层项目最新版

监控程序最新版(监控程序是比较稳定的,但是有可能会时不时更新一些细节,请保持使用监控程序的最新版):

https://github.com/thu-cs-lab/supervisor-rv

获取最新版的源代码之后务必阅读 README.md 文件。

硬件开发的顶层项目:

https://github.com/thu-cs-lab/thinpad_top

此硬件开发的顶层项目已经标注了开发板的输入输出信号,并有相应的注释,管脚的约束文件(xdc 文件,见后文)也已经提供。在实验的过程中,只需要在这个顶层开发项目中插入代码即可。