共通 - 处理器实验概述

实验目标

本实验的目的是在做较为复杂的能够运行监控程序的五级流水线处理器之前,让同学们通过一个简单的处理器设计来对每一条指令的执行有一个直观的感受。本实验的处理器与大实验基本类似,但只需要支持少数的指令即可。

由于本实验并不限制大家一定要实现多周期或者流水线 CPU,因此后面的实验文档将分为共通部分,以及流水线/多周期单独的部分以供大家参考。

在本实验中要实现的 CPU 需要支持的汇编程序如下:

addi t0, zero, 0 # loop variable

addi t1, zero, 100 # loop upper bound

addi t2, zero, 0 # sum

loop:

addi t0, t0, 1

add t2, t0, t2

beq t0, t1, next # i == 100?

beq zero, zero, loop

next:

# store result

lui t0, 0x80000 # base ram address

sw t2, 0x100(t0)

lui t0, 0x10000 # serial address

.TESTW1:

lb t1, 5(t0)

andi t1, t1, 0x20

beq t1, zero, .TESTW1

# do not write when serial is in used

addi a0, zero, 'd'

sb a0, 0(t0)

.TESTW2:

lb t1, 5(t0)

andi t1, t1, 0x20

beq t1, zero, .TESTW2

addi a0, zero, 'o'

sb a0, 0(t0)

.TESTW3:

lb t1, 5(t0)

andi t1, t1, 0x20

beq t1, zero, .TESTW3

addi a0, zero, 'n'

sb a0, 0(t0)

.TESTW4:

lb t1, 5(t0)

andi t1, t1, 0x20

beq t1, zero, .TESTW4

addi a0, zero, 'e'

sb a0, 0(t0)

.TESTW5:

lb t1, 5(t0)

andi t1, t1, 0x20

beq t1, zero, .TESTW5

addi a0, zero, '!'

sb a0, 0(t0)

end:

beq zero, zero, end

# loop forever, let pc under control

需要实现的指令如下表:

关于指令的详细功能,可以参考以下两节的内容:

-

简介参考资料中的 RISC-V spec

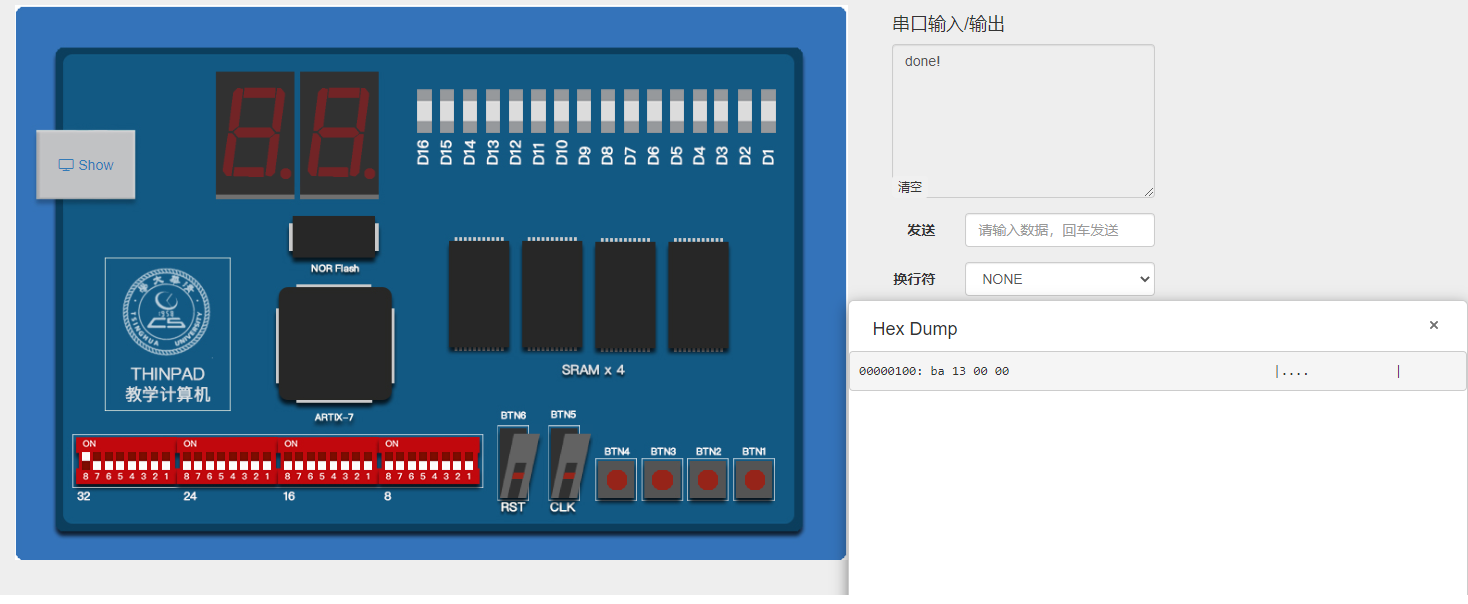

在云平台上预期的效果如下:

可以看到在串口上能够看到"done!"的输出,同时在 BaseRAM 的0x100地址处可以看到0x13ba=5050的结果,以小端方式存储。

关于云平台的操作方式,请参考:云平台使用指南

关于仿真的方式,请参考:Vivado 开发环境中的仿真

最后更新:

2023年8月31日

作者: