实验 3:SRAM 控制器实验

存储器系统是计算机中存放程序和数据的场所,分为内存和外存。ThinPAD-Cloud 教学计算机设置了两组 SRAM 作为内存。本实验主要完成内存存储器的读写访问过程。

模板文件

本实验的顶层模块模板:thinpad_top.srcs/sources_1/new3/lab3_top.sv

实验目的

- 熟悉 ThinPAD-Cloud 教学计算机内存储器的配置及与总线的连接方式;

- 掌握教学机内存(SRAM)的访问时序和方法;

- 理解总线数据传输的基本原理。

实验内容

使用教学计算机上的 FPGA 芯片,设计一个 Wishbone 协议的 SRAM 控制器,完成对存储器 SRAM 的访问。

在完成 SRAM 控制器之前,你需要阅读本实验的文档:

- SRAM:讲解了 SRAM 相关的信号和 SRAM 的读写时序

- Wishbone 总线协议:介绍了 Wishbone 协议的内容

- Wishbone SRAM 控制器:讲解了如何实现一个 Wishbone 协议的 SRAM 控制器

- 三态门:补充了三态门相关的知识

阅读完以后,就可以对着文档和提供的框架代码进行编写,你只需要编写 sram_controller 模块,无需修改 lab3_top 或 sram_tester,但强烈建议阅读它们,以便熟悉本实验的整体结构。

评测流程

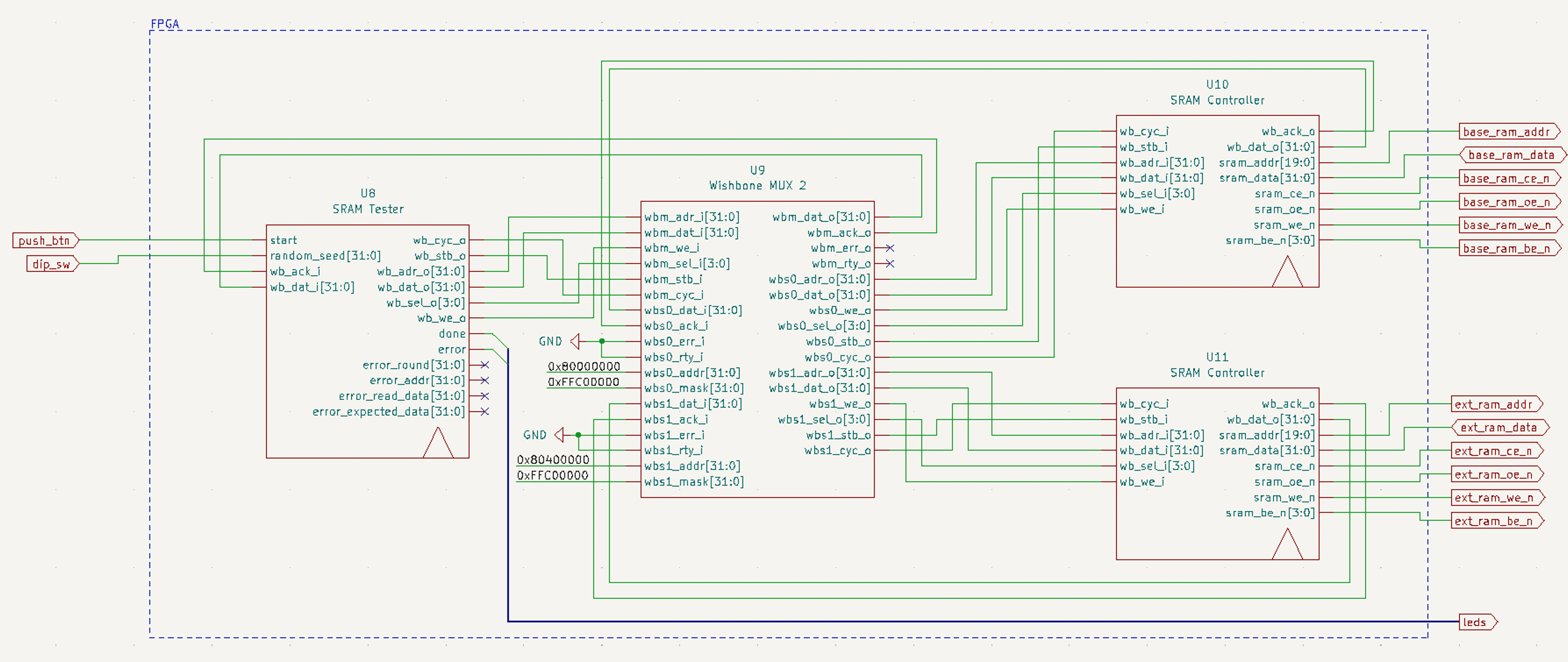

实验模板里提供了用于本实验的顶层模块 lab3_top。顶层模块例化了 sram_tester 模块,它会作为 Wishbone Master 向同学编写的 SRAM 控制器发起读或写请求,并且检查它的正确性。同时,顶层模块还例化了两次同学编写的 SRAM 控制器,分别用于控制 BaseRAM 和 ExtRAM。为了根据地址来区分要访问的是 BaseRAM 还是 ExtRAM,实验模板中提供了 wb_mux_2 模块,表示 1 个主接口到 2 个从接口(简称 1M2S)的多路复用器。

flowchart LR

sram_tester --> wb_mux;

wb_mux --> sram_controller_base;

wb_mux --> sram_controller_ext;测试模块 sram_tester 的行为是:

- 等待

push_btn按下; - 当

push_btn按下的时候,从拨码开关读取随机数生成器的种子; - 随机数生成器不断生成新的随机数;

- 根据随机数生成若干个内存的读和写请求;

- 向同学编写的 SRAM 控制器发起请求;

- 检查请求的行为是否符合要求。

内存数据验证

在实验的过程中,在线的程序将在每轮测试结束后,读取 BaseRAM 和 ExtRAM 存储器中的数据,并与预期数据比较。

评测提示

评测脚本使用的随机数种子固定为 0x1。在线实验调试时,为了与自动评测现象一致,需要将最右侧的拨码开关设置为 ON 位置,即将随机种子设置为 0x1。该情况下,使用内存总线分析功能,获取到的访存序列开头如下:

访存序列

平台上的“内存总线分析”功能,仅支持对 BaseRAM 的访问记录,不支持 ExtRAM 的访问记录。因此,此处看到的访存序列,与仿真中的不完全一致,只包含 Wishbone 地址为 0x8000_0000 至 0x803F_FFFF 的访问记录。

此外,工具显示的地址单位为 byte,由于 SRAM 的数据线宽度为 32 位,此处显示的应该是 Wishbone 地址,抹去最后两位的数据。

原理图

实验步骤

本实验的完成需要用 FPGA 芯片来控制存储芯片的读写,根据实验要求,需要在 FPGA 中实现 Wishbone 协议的 SRAM 控制器。具体步骤如下:

-

做好准备: a. 阅读本实验前的相关内容介绍; b. 阅读提供的框架代码

lab3_top.sv。 -

定义状态机: a. 根据 SRAM 文档设计状态机; b. 实现读和写两种请求的状态机状态转移流程。

-

仿真测试: a. 在 Vivado 中启动仿真; b. 观察仿真中总线的请求过程; c. 调试直到仿真中的行为符合预期。

-

上板验证: a. 将编译好的设计烧入实验板; b. 拨动拨码开关预设一个值,这个值作为随机数生成器的初始种子; c. 打开实验平台的内存总线录制功能; d. 按下按钮,启动一次随机的内存访问; e. 观察 LED 灯显示的评测结果; f. 观察录制的内存访问历史; g. 记录实验结果。

按钮极性

实验板上拨码开关 SW1~SW32 是 ON 端表示 1,相反表示 0;时钟和复位按钮 CLK、RST 均是按下为 1,放开为 0。

思考题目

- 静态存储器的读和写各有什么特点?

- 什么是 RAM 芯片输出的高阻态?它的作用是什么?

- 本实验完成的是将 BaseRAM 和 ExtRAM 作为独立的存储器单独进行访问的功能。如果希望将 Base_RAM 和 Ext_RAM 作为一个统一的 64 位数据的存储器进行访问,该如何进行?

实验提示

本实验最重要的一点是对于 SRAM 说明书中读写时序的理解,只有正确理解了时序,按照说明书的要求给出信号,SRAM 就可以正确地响应。因此,在实验之前必须阅读和理解一下 SRAM 的说明书,理解一下时序的概念。

常见的错误:

-

注意,在 Thinpad 实验平台中,内存是按照字编址的(不是按照字节编址的),字的位宽是 32 位,但是在 RISC-V 中是按照字节寻址的。因此,这里面两者是有差异的,需要考虑如何把对于字节的访问翻译为对应的对于字的访问(当然需要配合字节的使能信号)。在本实验中体现不明显,在后面的处理器实验中必须要考虑到这一点。

-

如果使用云平台上的读写内存的工具,在进行读写的时候 FPGA 内部的电路会被清空,在读写完成之后会重新写入 FPGA,这个时候整个系统就跟刚刚把 bit 文件下载到 FPGA 中一样。

实验报告要求

-

给出你的 SRAM 状态机设计,并解释每个状态对应的功能。

-

设定一个随机种子进行仿真,给出部分仿真波形,初步说明设计的正确性。

-

在云平台上使用与第 2 步中相同的种子进行实验,使用云平台工具记录前 20 次读写操作,与仿真结果进行比较。

-

回答思考题。