PLL

进阶功能

本章节属于拓展功能,其主要目的是给大家一个做一个简单的进阶参考。进阶实验的目的是锻炼大家的自学能力。因此对本章节内容的答疑可能不会被接受。特此声明。

在我们的实验板子上提供的时钟有 50MHz 和 11.0592MHz 两个。然而在前面的实验的过程中,我们实际使用的是 10MHz 的时钟。

大家在数字逻辑课上应该都学过一些简单的分频方法,如二分频,四分频等等。但我们实际使用的时钟可能是各种频率的,比如非整数倍,增频等等。应该如何生成各种频率的时钟呢?PLL (Phase Locked Loop, 锁相环) 就可以解决这个问题。

我们不需要了解 PLL 的内部实现。下面将介绍在 Vivado 中如何使用 PLL IP 核来生成不同频率的时钟。

引入 IP 核

在使用每个 IP 核之前,我们需要在 Vivado 的 IP 核目录中找到对应的 IP 核,将其加入到工程中,步骤如下:

-

单击左侧的

IP Catalog进入 IP 核目录

-

搜索

Clocking找到Clocking Wizard并双击

-

在配置的第一页配置模块名称和输入时钟频率。同时可以在左侧看到模块的输入输出图。惯例:一般左侧为输入信号,右侧为输出信号。

在这里我们将下面的输入频率配置为板子的时钟频率 50.000 MHz

-

点击

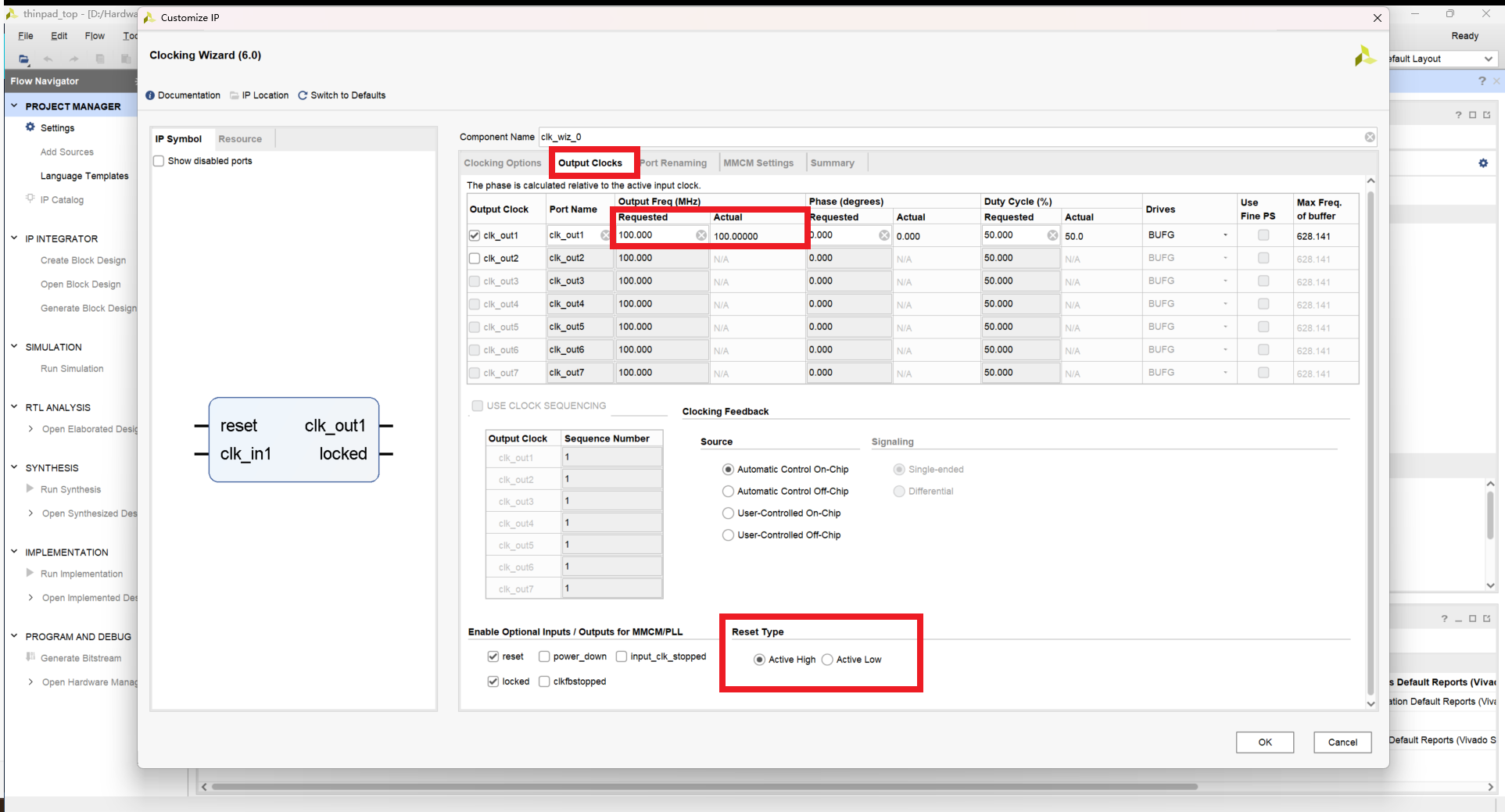

Output Clocks进入配置第二页。 在这里我们可以更改输出时钟个数,输出频率,时钟相位,时钟的占空比等等。而右下角可以调整输入的rst为 0 使能还是 1 使能。

在这里,我们配置输出频率为 10 Mhz,不改变相位和占空比。而

rst使能方面,由于我们使用板子上的reset_btn按键开关进行控制,因此选择 1 使能。在设置完输出频率之后,可以在

Actual一栏看到实际输出的时钟频率。 -

点击

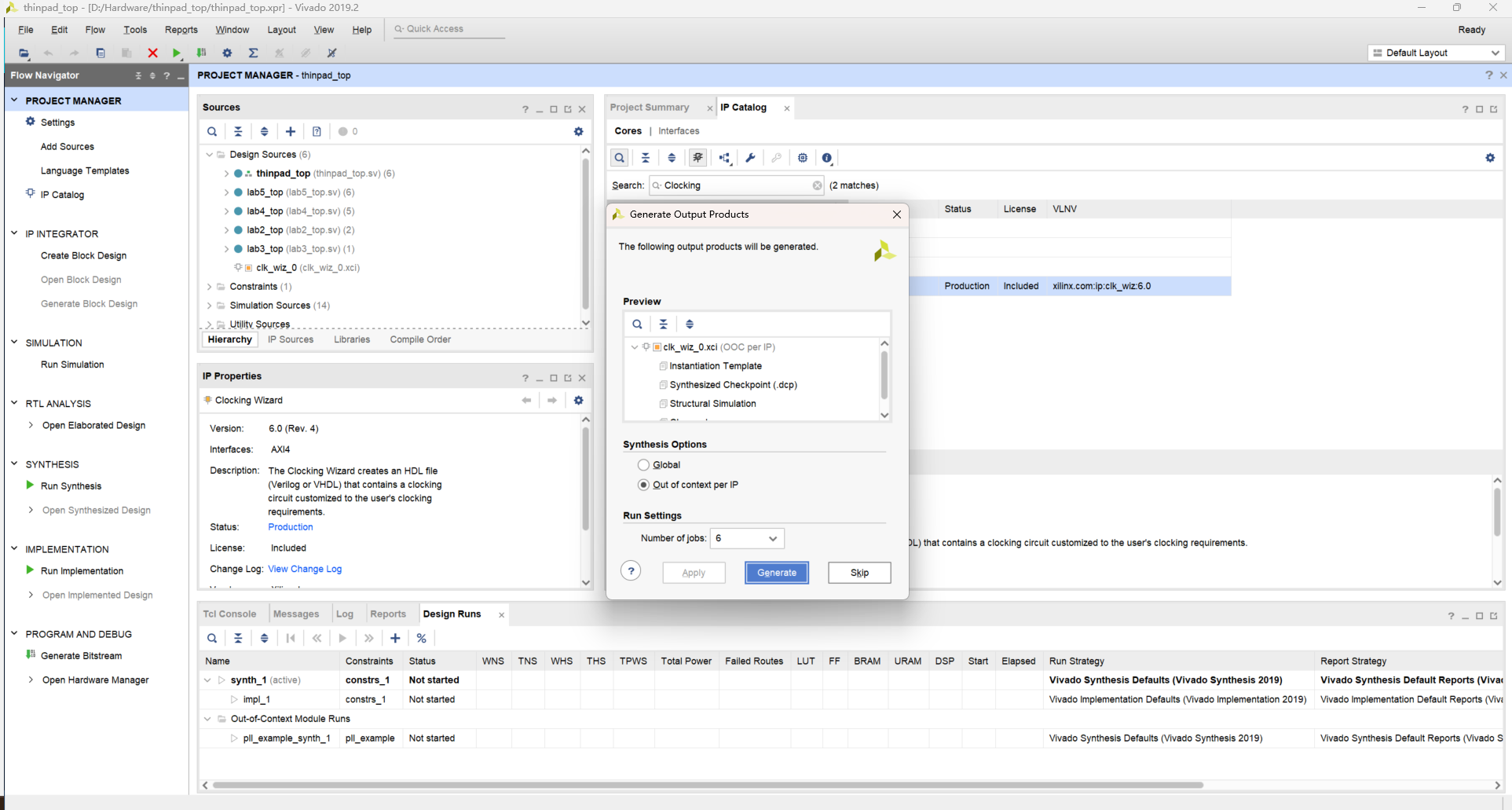

OK,弹出对话框询问你是否生成 IP 核对应代码。

单击

Generate生成。 -

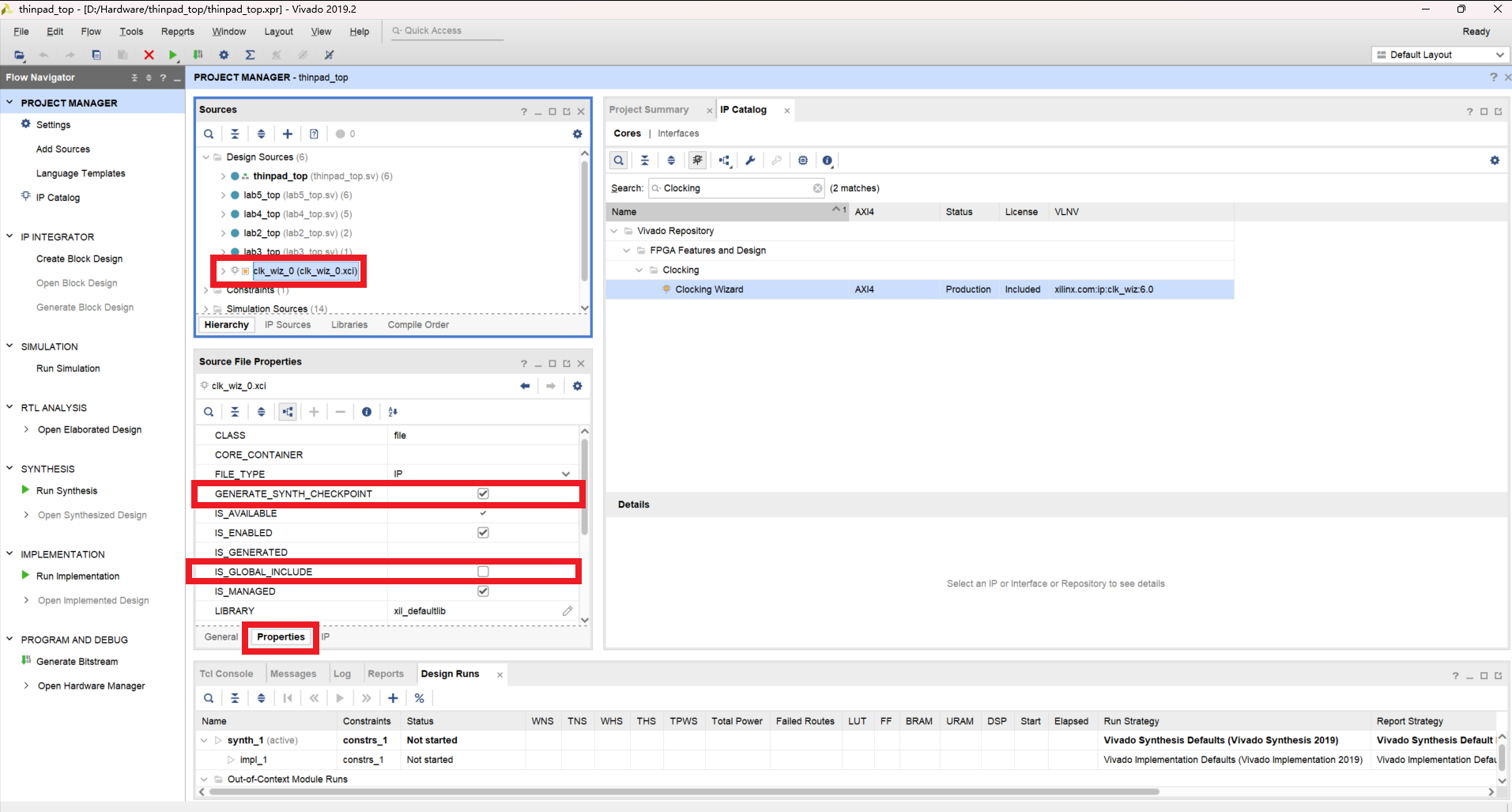

在左侧可以看到生成的 PLL IP 核,单击,然后在边栏中点击

Properties,确认GENERATE_SYNTH_CHECKPOINT和IS_GLOBAL_INCLUDE两个选项选上。否则可能会导致有部分 IP 核加入工程但未在设计中使用导致 CI 失败。对于所有的 IP 核都需要做这一步

-

之后就可以在设计中例化使用了。

注意到实验模板中 10MHz 频率的时钟也是由这个 IP 核生成的 (与上述过程配置几乎相同,多一个 20MHz 的生成时钟) 。因此接下来我们将结合模板中例化的 IP 核进行说明。

PLL 信号说明

各个模板中,pll 例化的部分如下:

// PLL 分频示例

logic locked, clk_10M, clk_20M;

pll_example clock_gen (

// Clock in ports

.clk_in1(clk_50M), // 外部时钟输入

// Clock out ports

.clk_out1(clk_10M), // 时钟输出 1,频率在 IP 配置界面中设置

.clk_out2(clk_20M), // 时钟输出 2,频率在 IP 配置界面中设置

// Status and control signals

.reset(reset_btn), // PLL 复位输入

.locked(locked) // PLL 锁定指示输出,"1"表示时钟稳定,

// 后级电路复位信号应当由它生成(见下)

);

logic reset_of_clk10M;

// 异步复位,同步释放,将 locked 信号转为后级电路的复位 reset_of_clk10M

always_ff @(posedge clk_10M or negedge locked) begin

if (~locked) reset_of_clk10M <= 1'b1;

else reset_of_clk10M <= 1'b0;

end

可以看到,在上述配置下 pll 模块的输入输出信号线共 5 条:

clk_in1输入标准时钟clk_out1输出时钟 1 , 根据配置为 10MHzclk_out2输出时钟 2 , 根据配置为 20MHzreset输入复位信号,根据配置为 1 使能locked输出锁定信号,输出 1 时表示时钟稳定可以使用。因此,当其下降沿时,应该将后续电路复位信号设置为 1。

更详细的说明和使用方法可以去 Xilinx 官方文档网站查看: PLL 文档