实验准备与主要操作流程

实验目标

完成本实验后,你应能够:

- 使用 AI-Coder 完成 FPGA 开发全流程。

- 实现四位全加器,并完成仿真验证与硬件测试。

- 借助 AI 分析 Vivado 报错并修复常见问题。

使用前提醒

本实验在 VS Code 网页端 完成。每位同学会分配独立容器,请按照网络学堂分发的网址登录测试,并提前确定工作目录,确保 Vivado 能正常运行。

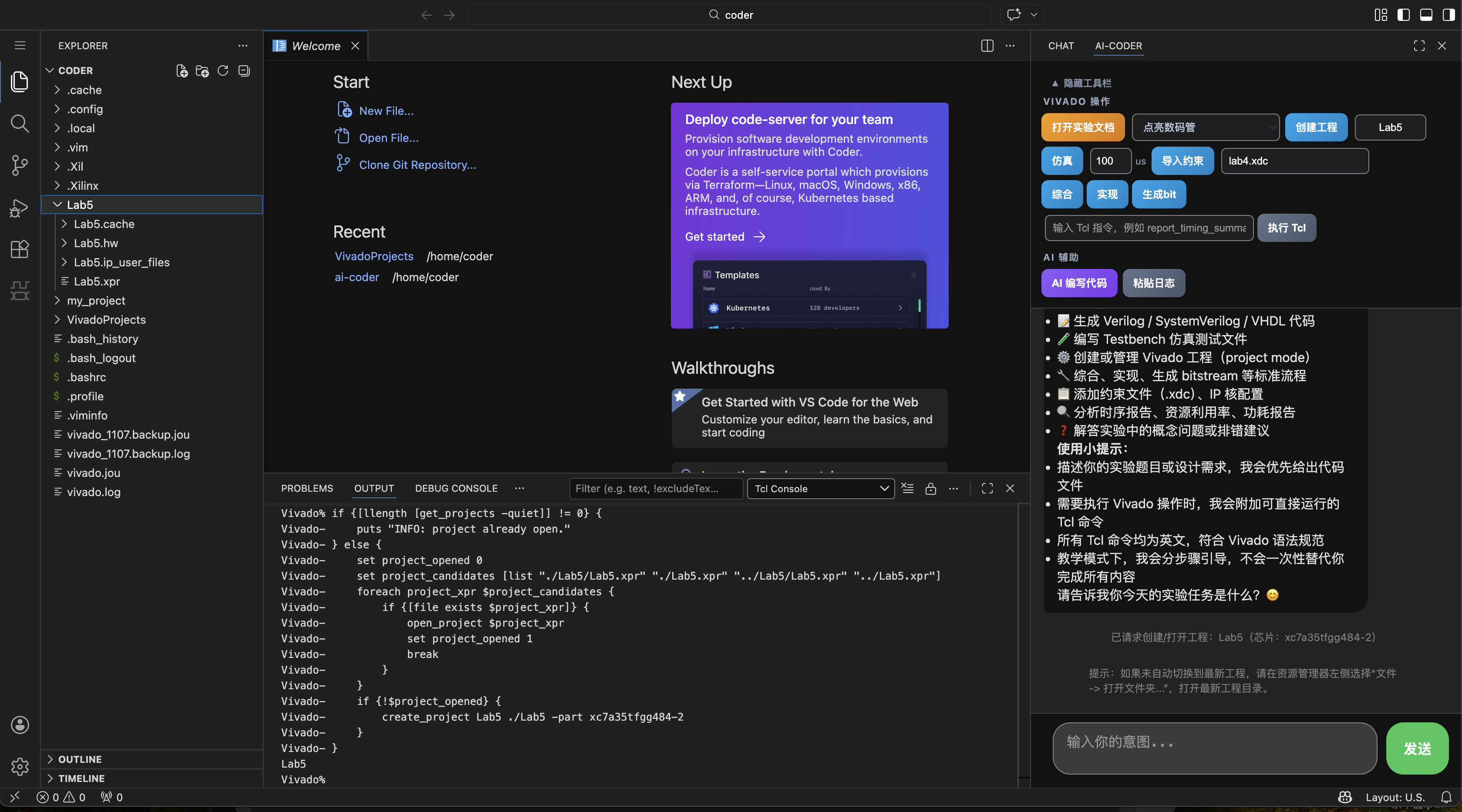

点击左侧边栏的 AI-Coder 图标即可打开插件面板:

建议右键点击左侧边栏的 AI-Coder 图标,选择 移动到右侧边栏,避免切换代码或波形页面时插件会话被自动回收。

持久化存储目录

只有 ~/,即 /home/coder/ 内的文件会被持久化存储。其他路径下的文件可能随 Docker 重启而消失,建议在 ~/VivadoProjects 下创建新工程。

路径和命名要求

工程目录、文件名、模块名和路径只建议使用英文、数字、下划线。不要使用中文、空格或特殊字符(如 @、中文括号等),否则可能出现编译或运行错误。

创建 / 打开 Vivado 工程

插件默认在当前 VS Code 工作区下创建工程。若已存在同名工程,插件会直接打开旧工程;如需重新创建,请先手动删除旧工程文件夹。

- 在 AI-Coder 面板顶部找到 “创建工程” 按钮,旁边有工程名输入框。

- 将输入框改为你想要的工程名,例如

Lab5。 - 点击 “创建工程” 按钮。

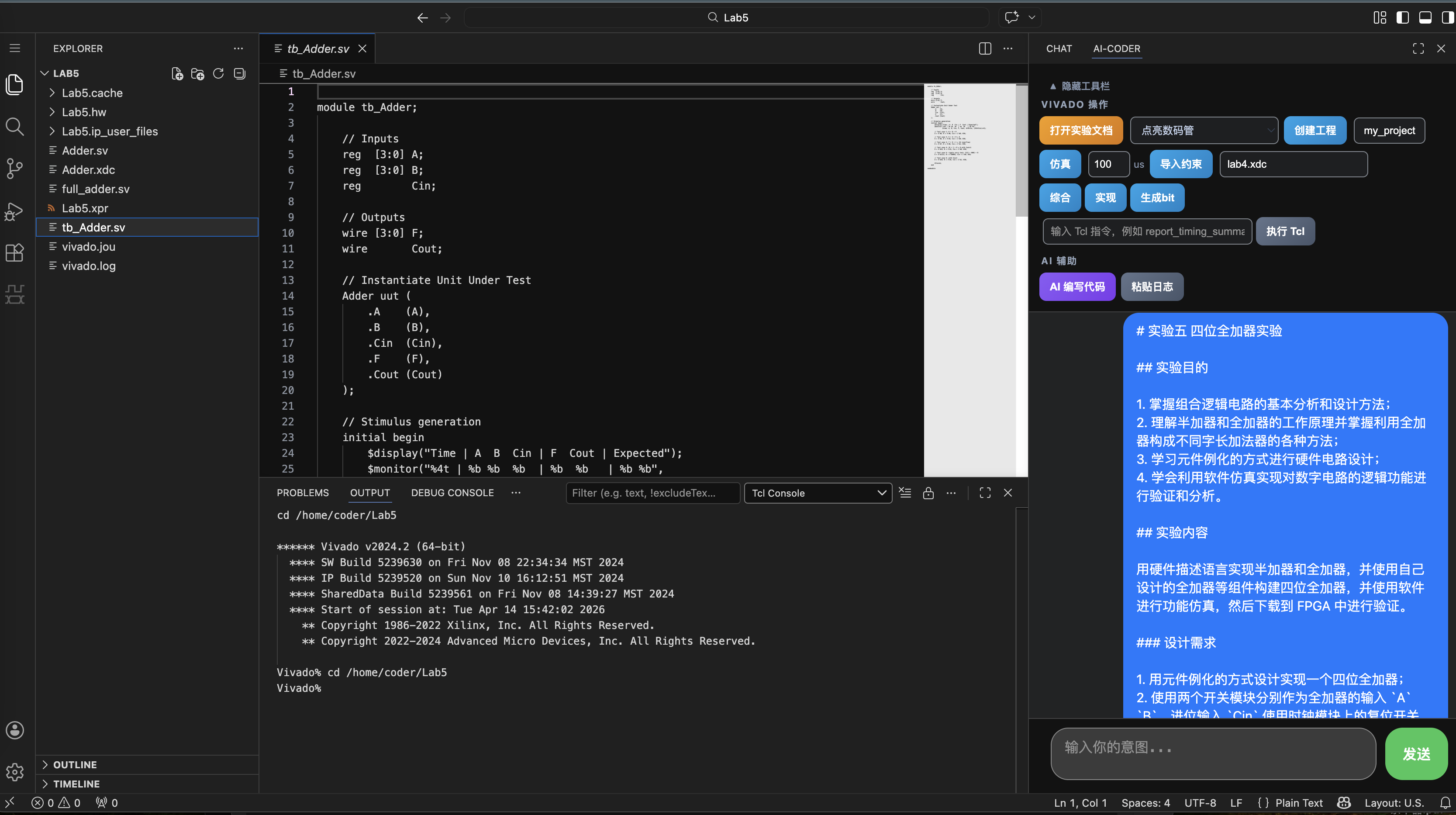

如下图,可以看到已经创建 Lab5 工程:

默认芯片型号

插件默认使用 xc7a35tfgg484-2,与实验箱 FPGA 型号一致。

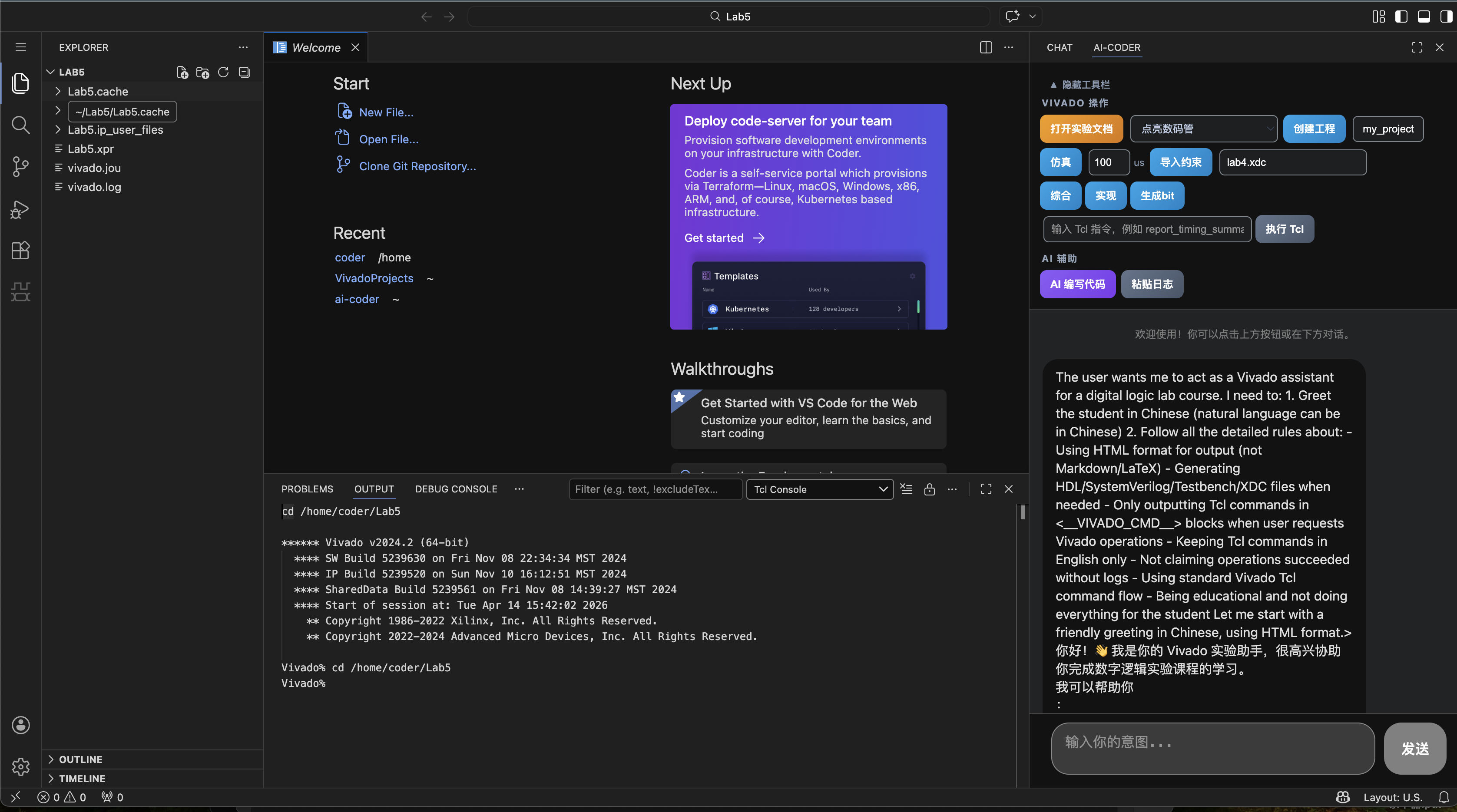

切换工程目录并阅读实验文档

每个实验应使用独立子文件夹。实验前请先打开对应子文件夹作为 VS Code 工作区,再进行后续操作。

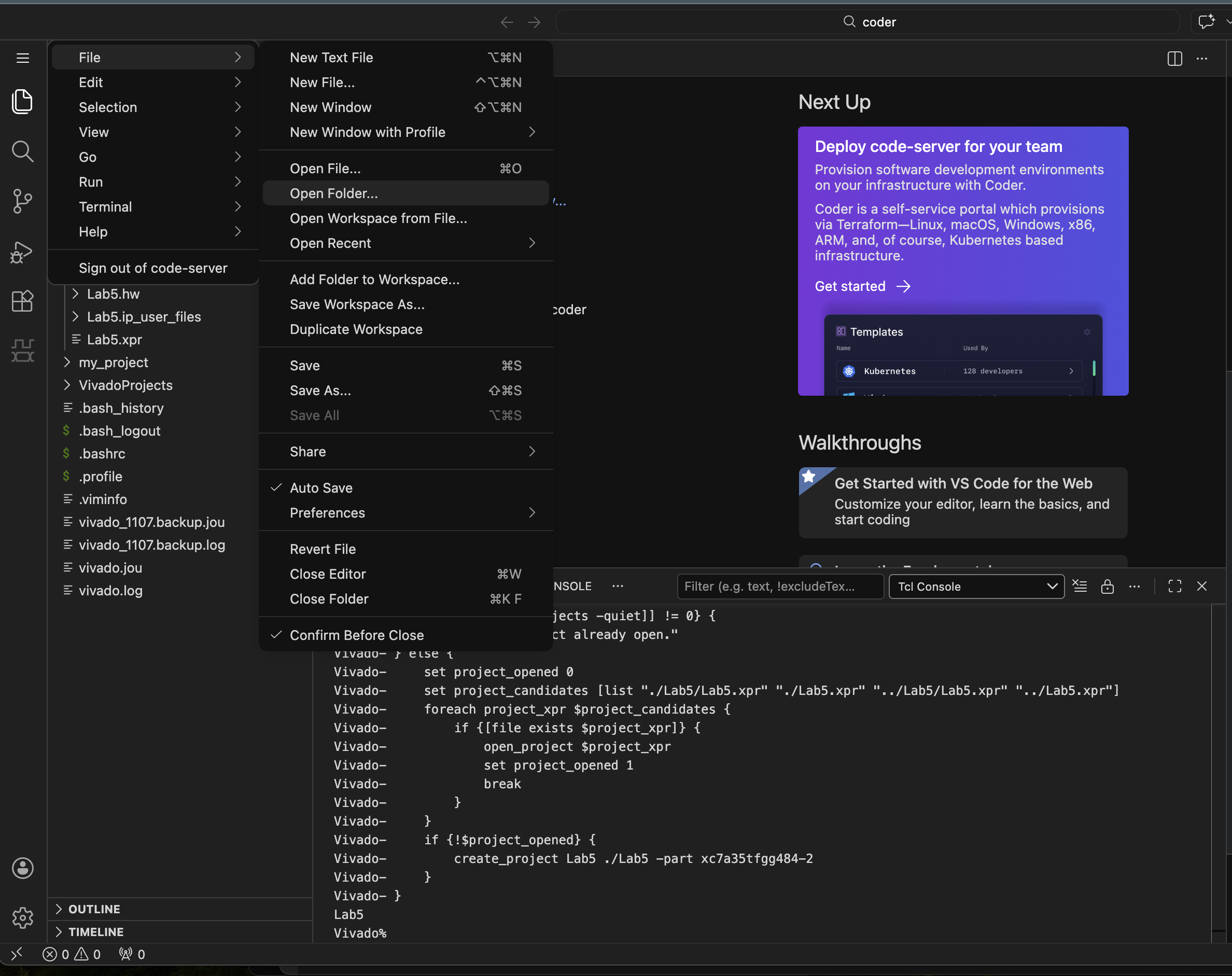

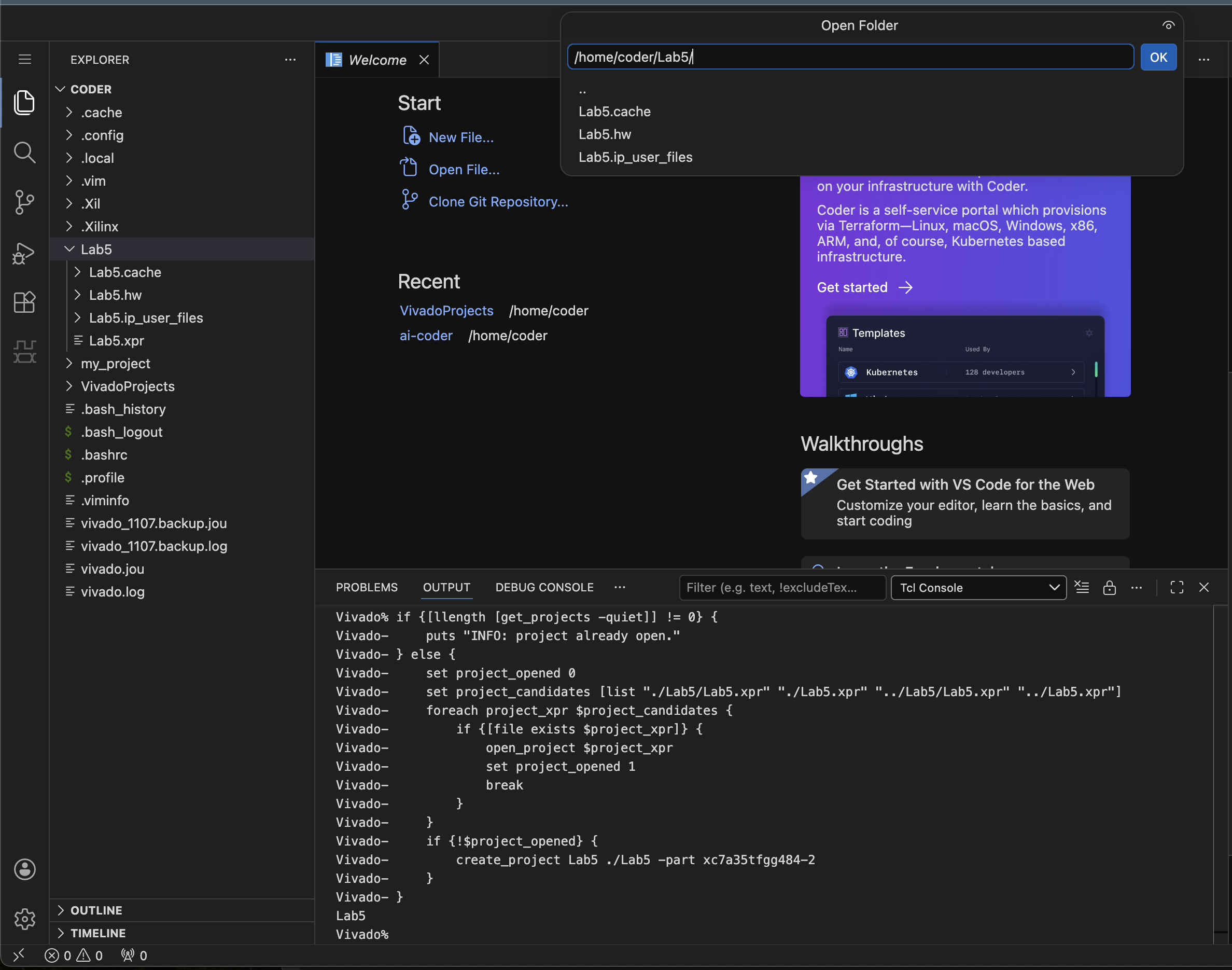

-

在 VS Code 菜单中选择

文件 -> 打开文件夹...,打开最新工程目录,例如Lab5。

-

在 Vivado 操作区点击 “打开实验文档”。

- 在下拉框选择

四位全加器,浏览器会打开对应实验页面。

使用 AI 编写代码与 testbench

方式一:一键生成(推荐)

-

在底部输入框中粘贴本次实验的设计需求,以及 实验五 四位全加器 中给定的参考代码。例如:

实验五:四位全加器。 用元件例化的方式设计实现一个四位全加器。 先编写一位全加器 full_adder(输入 A、B、Cin,输出 F、Cout), 再用 4 个 full_adder 例化组成四位全加器 Adder(输入 A[3:0]、B[3:0]、Cin,输出 F[3:0]、Cout)。 同时编写 Testbench 进行功能验证。 管脚约束:A[3:0] 对应 IO1~IO4,B[3:0] 对应 IO6~IO9,Cin 对应 IO5, F[3:0] 对应 IO17~IO20,Cout 对应 IO16。 -

点击 “AI 编写代码” 按钮,或直接点击 “发送”。

生成代码后的示意图如下:

AI 通常会生成以下文件并写入工作目录:

| 文件 | 说明 |

|---|---|

full_adder.sv |

一位全加器模块 |

Adder.sv |

四位全加器顶层模块 |

Adder_tb.sv |

仿真测试文件 |

Adder.xdc |

管脚约束文件 |

testbench 命名限制

当前实现检测 testbench 并加入仿真 sim_1 时有命名要求:文件名需匹配 tb*.v、*_tb.v、tb*.sv 或 *_tb.sv。建议让 AI 生成前先约定好文件名。

不要直接信任 AI 生成的约束

AI 生成的 XDC 约束可能与实验箱管脚不一致。建议直接使用实验文档中的官方约束覆盖 AI 生成的 XDC 文件。

方式二:对话式逐步生成

你也可以通过多轮对话逐步完善设计:

- 先发送:

请帮我编写一位全加器 full_adder。 - 确认无误后,再发送:

用 4 个 full_adder 例化组成四位全加器 Adder。 - 接着发送:

为 Adder 编写 Testbench,覆盖多组输入组合。 - 最后发送:

生成 XDC 约束文件,A[3:0] 对应 IO1~IO4,B[3:0] 对应 IO6~IO9……。

AI 自动写文件

AI 回复中如果包含文件块,插件会自动将文件内容写入工作目录。你可以在 VS Code 文件浏览器中看到新生成的文件。

设置顶层

第三步生成代码和 testbench 后,建议顺手设置一次顶层,减少工程配置错误。

“设置顶层”区域位于 “仿真” 按钮附近,包含:

- 顶层名输入框。

fileset选择框:sources_1/sim_1。- “设置顶层” 按钮。

使用方法:

- 在输入框填写模块名,不要填写文件名。例如填

tb_adder,不要填tb_adder.v。 - 若设置设计顶层,选择

sources_1;若设置仿真顶层,选择sim_1。 - 点击 “设置顶层”,系统会自动执行设置并回读确认结果。

推荐用法

综合前可将 Adder 设为 sources_1 的顶层;仿真前可将 tb_adder 或 Adder_tb 设为 sim_1 的顶层。若仿真识别不到 testbench,可优先使用此按钮修正。

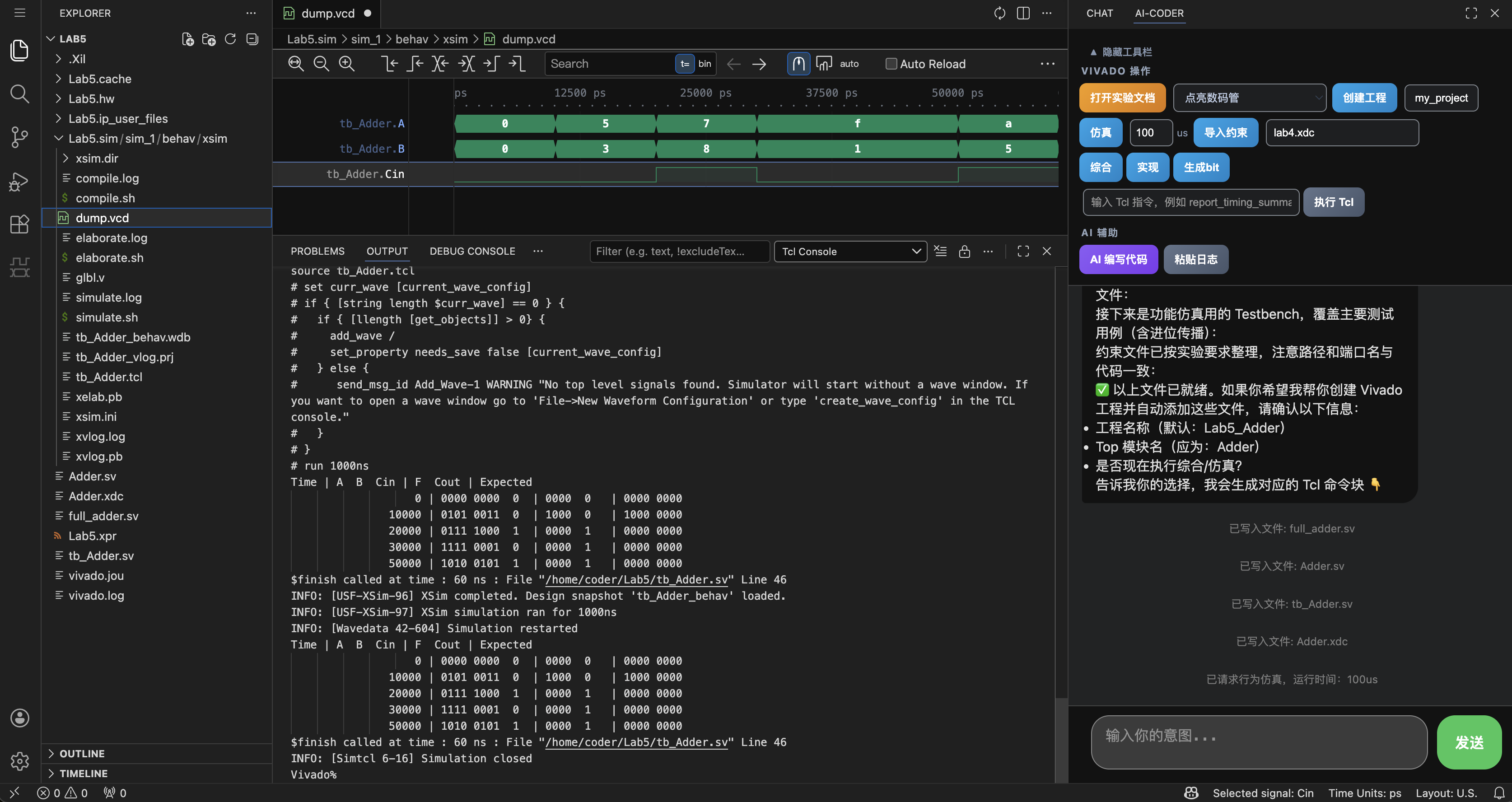

功能仿真

- 在 “仿真” 按钮旁设置时间,默认

100 us。 - 点击 “仿真”。

当前仿真流程会自动完成:

- 确保工程已打开。

- 扫描当前目录 Verilog 文件并分类加入

sources_1/sim_1。 - 自动更新编译顺序。

- 自动检查并尝试设置

sim_1 top。 - 执行仿真命令序列:

launch_simulation -> open_vcd -> restart -> log_vcd -> run xxxus -> close_vcd -> close_sim

仿真启动后会生成 dump.vcd 文件。你可以用 VaporView 插件打开波形,观察 A、B、Cin、F、Cout 等信号变化,验证全加器功能是否正确。标准 testbench 还应包含 cases test,可通过 Vivado 输出辅助 debug。

仿真成功的表现:输出部分没有 Error,testbench cases 均通过,且 Lab5_sim1 目录下出现 dump.vcd 波形文件。

previous response id

与 AI 交互时,系统会展示 prid。将其完整复制(包含 prid 前缀)到输入框并发送,可以回到以前对话的状态。

常见失败原因

如果提示 sim_1 top is empty,通常是 testbench 未识别或命名不匹配。请检查 testbench 文件名与模块名,也可以使用“设置顶层”按钮修正。

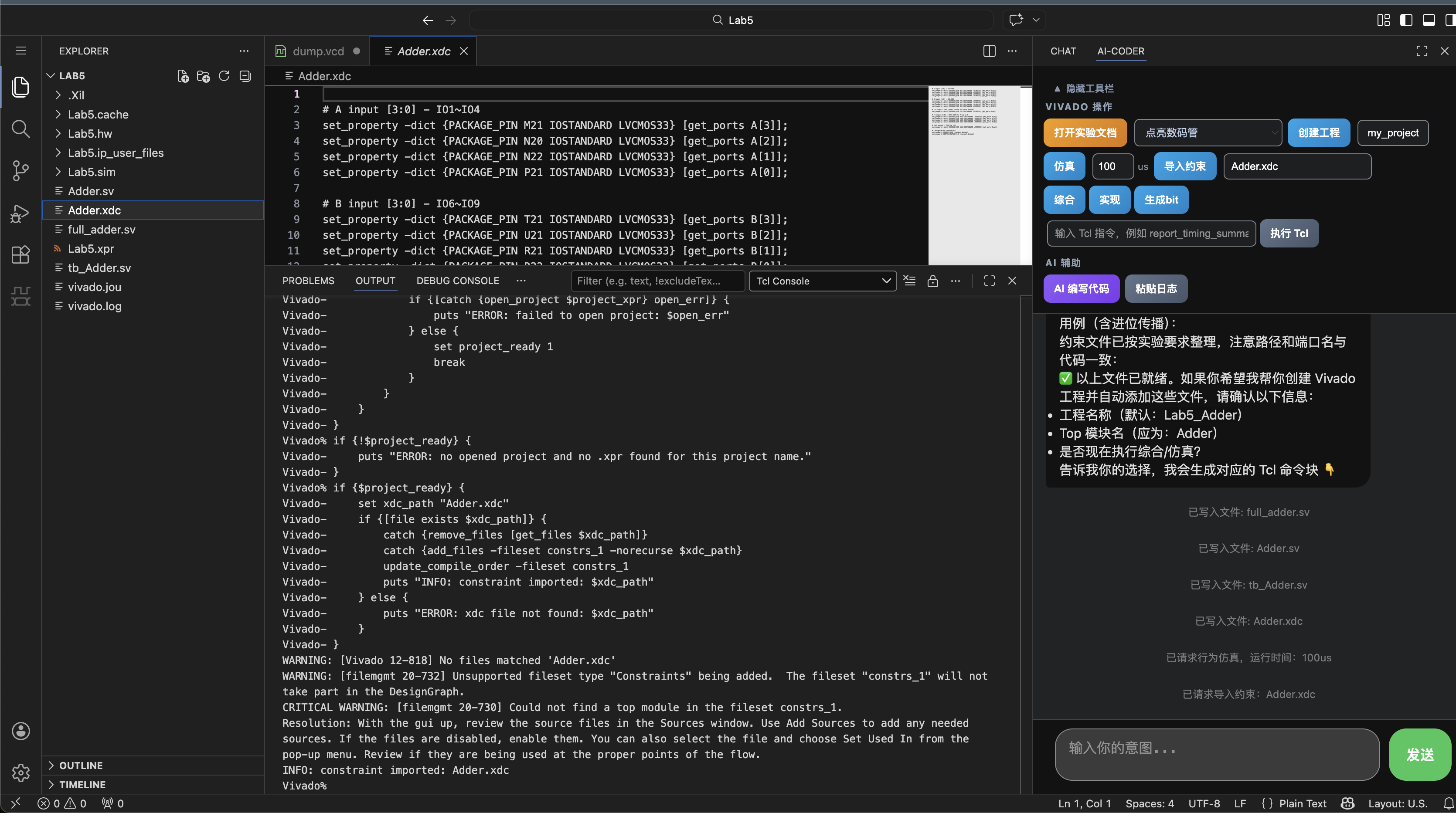

导入约束文件

- 在实验文档中找到管脚约束(XDC)部分,复制并保存为本地

.xdc文件,例如lab5.xdc。 - 在 “导入约束” 旁输入 XDC 文件路径,例如

lab5.xdc。 - 点击 “导入约束”。

插件会执行类似命令:

set xdc_path "lab5.xdc"

if {[file exists $xdc_path]} {

catch {remove_files [get_files $xdc_path]}

catch {add_files -fileset constrs_1 -norecurse $xdc_path}

update_compile_order -fileset constrs_1

}

若路径错误,会提示 xdc file not found。

以下展示了添加 Adder.xdc 的例子。若输出端无 Error,且出现 INFO: constraint imported: Adder.xdc,说明约束导入成功。

务必核对管脚映射

XDC 中的端口名必须与顶层模块完全一致,管脚也必须与 实验五 四位全加器 中给出的约束和实际硬件接线一致。

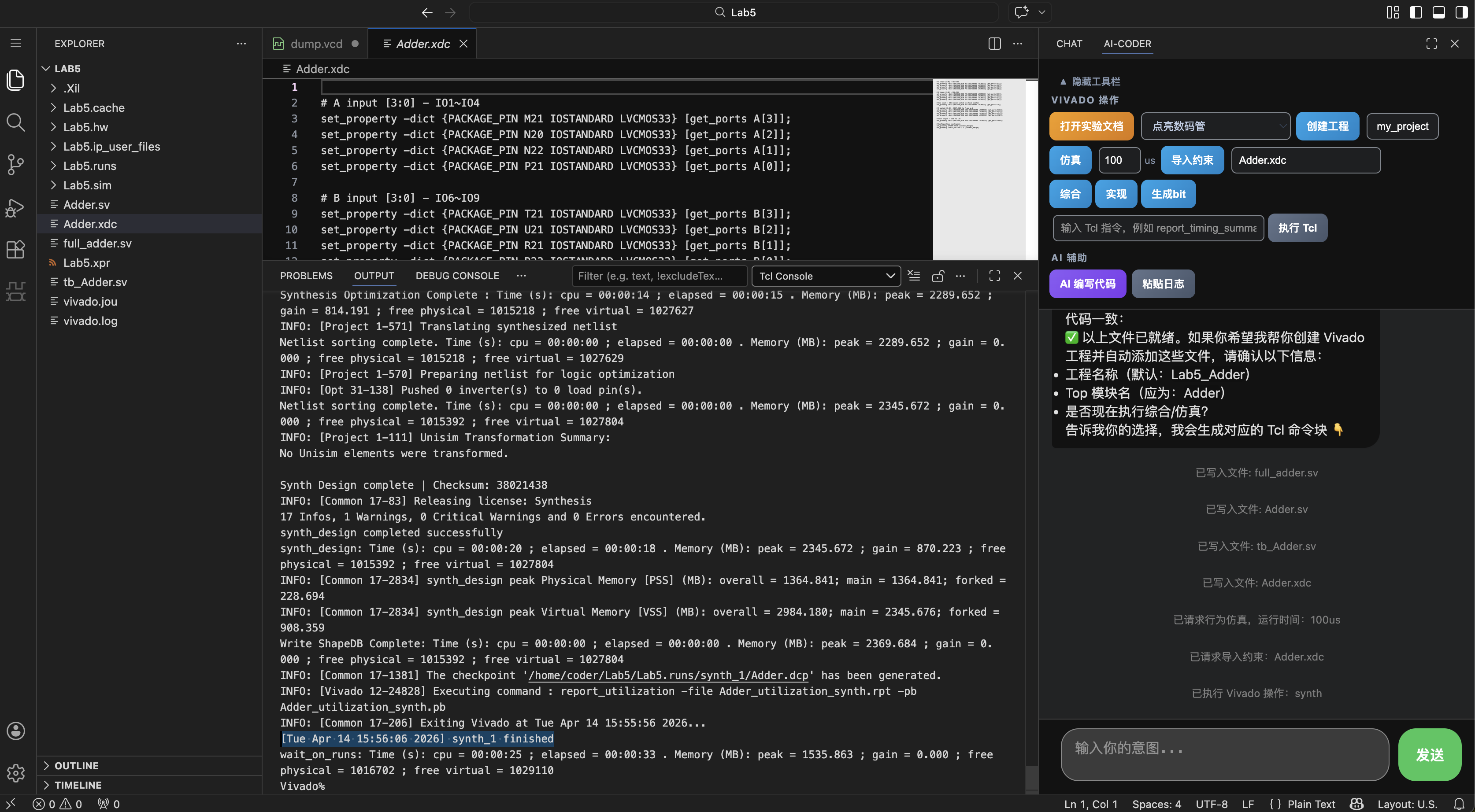

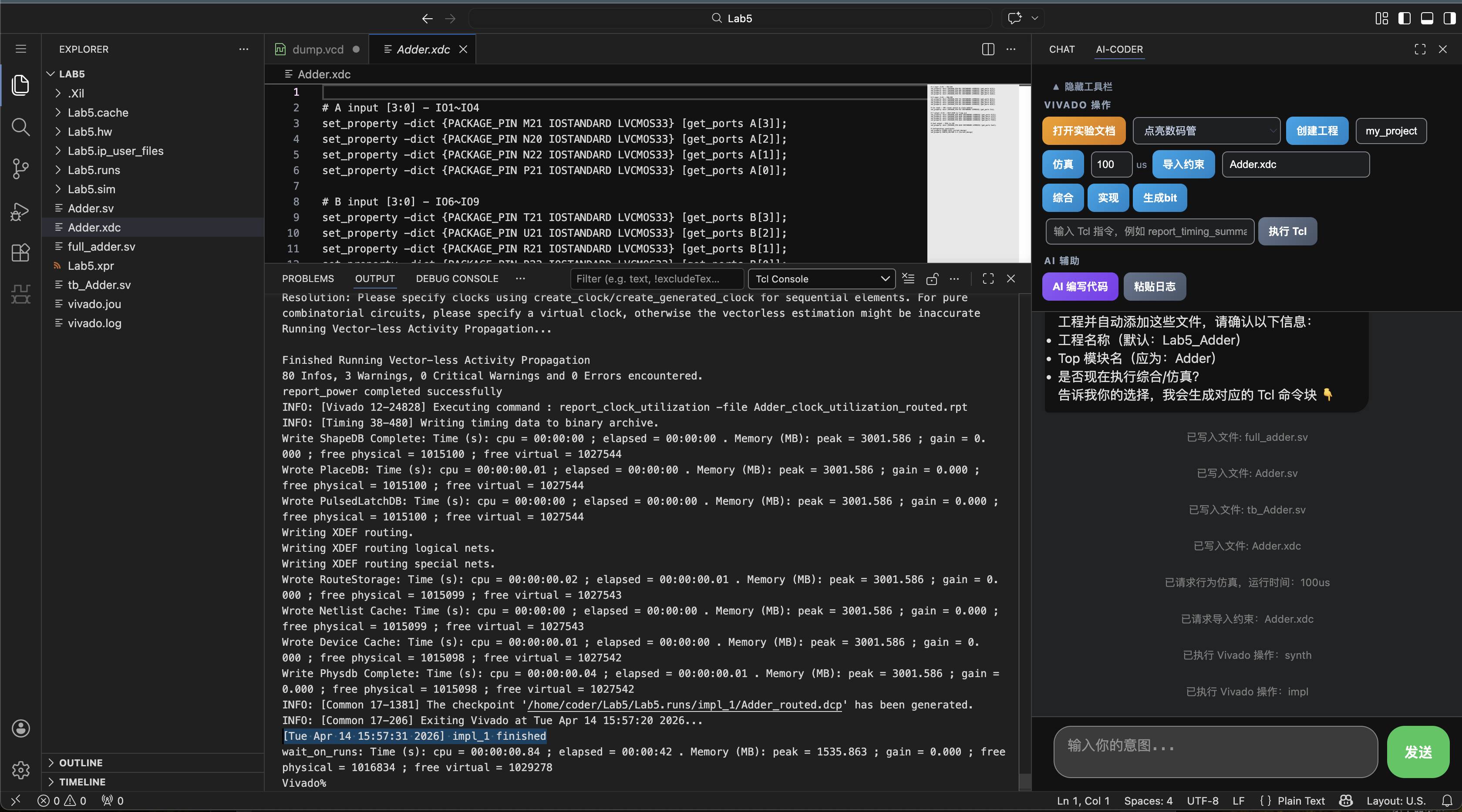

综合、实现与生成 bitstream

综合

点击 “综合” 按钮,插件会在确保工程打开后执行:

reset_run synth_1

launch_runs synth_1

wait_on_run synth_1

等待 Tcl Console 中出现 synth_1 complete,表示综合完成。

实现

点击 “实现” 按钮,执行:

reset_run impl_1

launch_runs impl_1

wait_on_run impl_1

等待 Tcl Console 显示 impl_1 complete,表示实现完成。

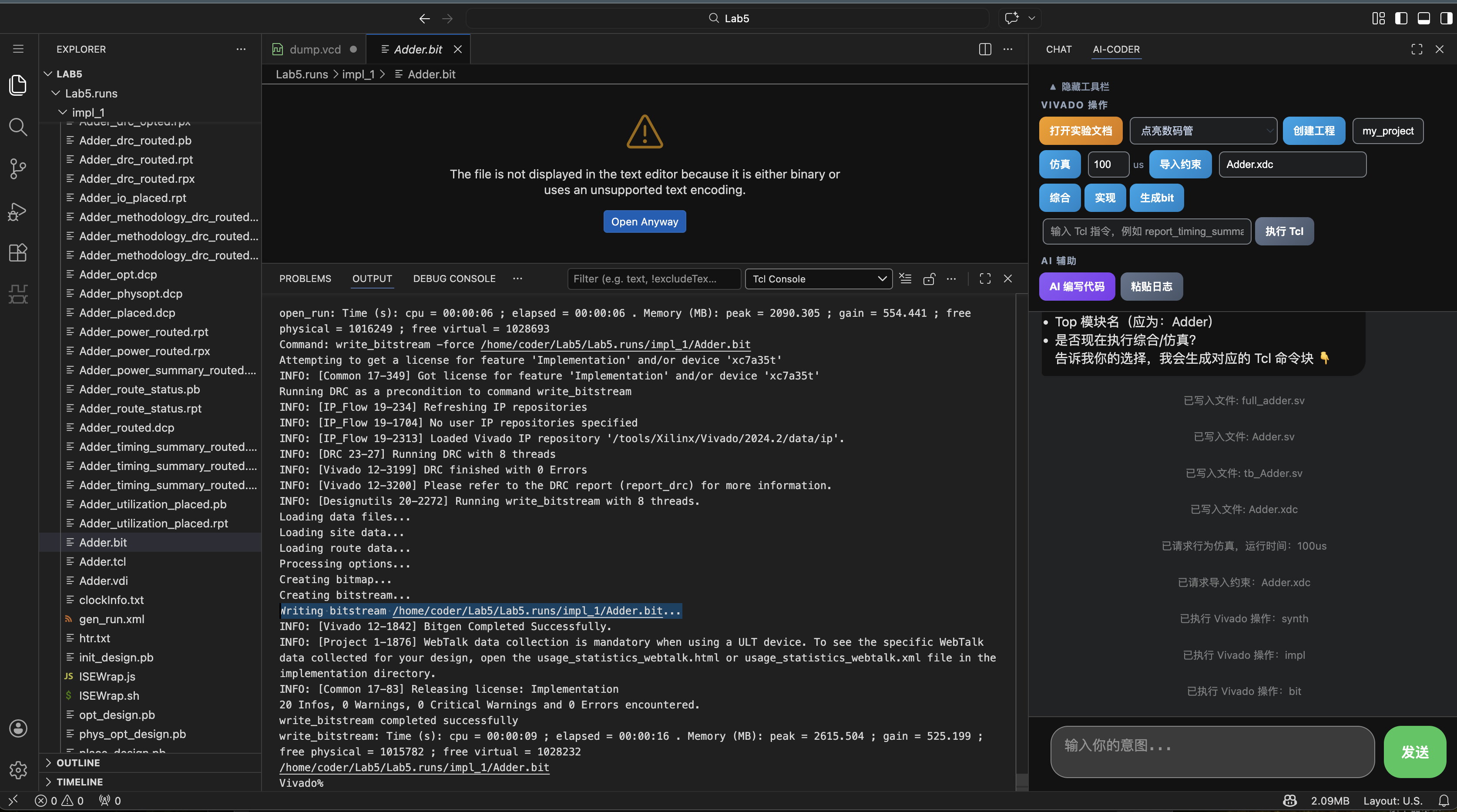

生成 bitstream

点击 “生成 bit” 按钮,执行:

open_run impl_1

write_bitstream -force [get_property DIRECTORY [current_run]]/[get_property TOP [current_fileset]].bit

生成完成后,.bit 文件会出现在工程目录的 impl_1 运行目录中,可用于下载到 FPGA。

若报 NSTD-1 / UCIO-1,说明约束未正确导入或端口名不匹配,请回到实验文档和约束文件两处检查。